THE 80286 INSTRUCTION SET

CMPS/CMPSB/CMPSW-Compare string operands

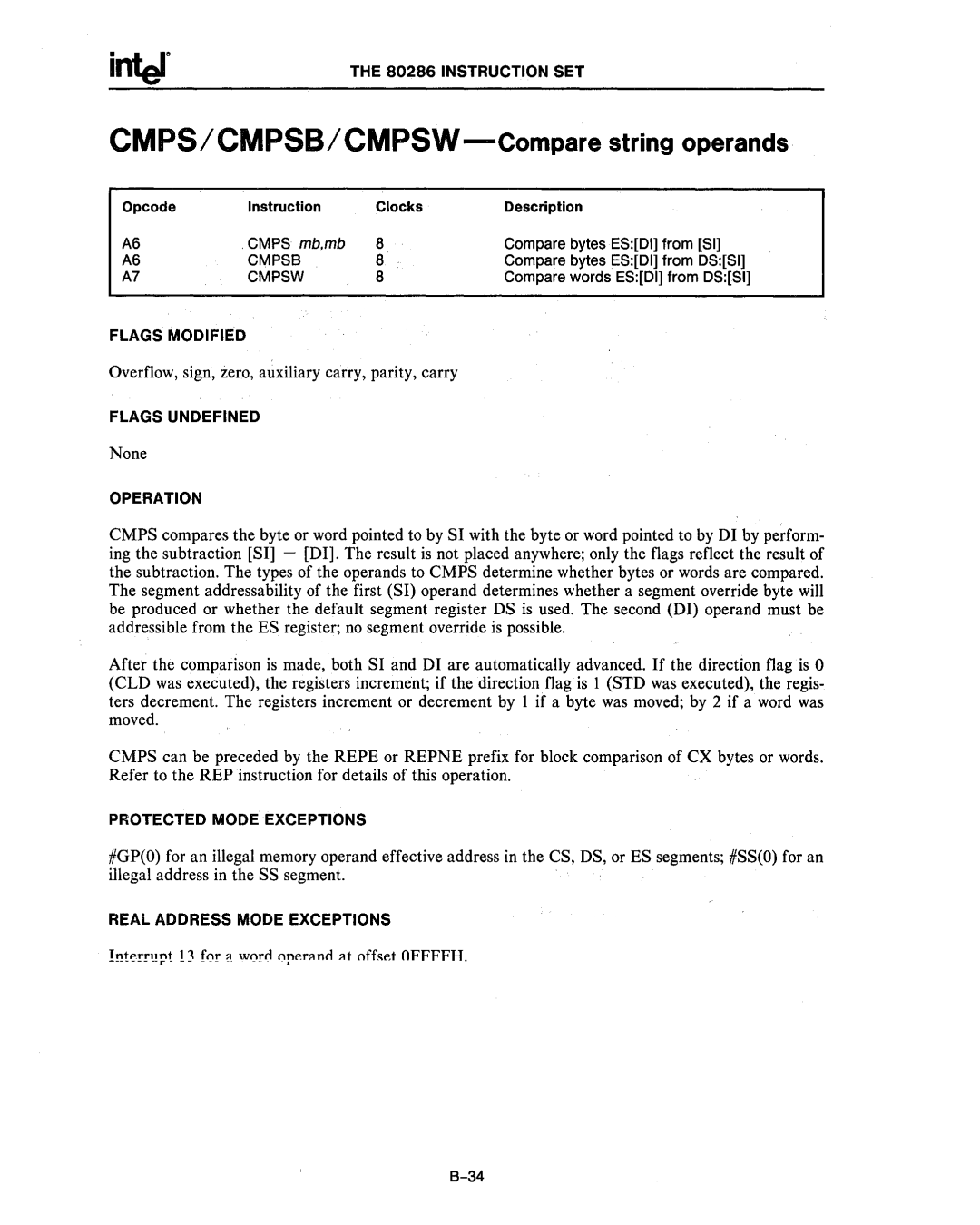

Opcode | Instruction | Clocks | Description |

A6 | .CMPS mb,mb | 8 | Compare bytes ES:[DI] from [SI] |

A6 | CMPS8 | 8 | Compare bytes ES:[DI] from DS:[SI] |

A7 | CMPSW | 8 | Compare words ES:[DI] from DS:[SI] |

FLAGS MODIFIED

Overflow, sign, zero, auxiliary carry, parity, carry

FLAGS UNDEFINED

None

OPERATION

CMPS compares the byte or word pointed to by SI with the byte or word pointed to by OI by perform- ing the subtraction [SI] - [OI]. The result is not placed anywhere; only the flags reflect the result of the subtraction. The types of the operands to CMPS determine whether bytes or words are compared. The segment addressability of the first (SI) operand determines whether a segment override byte will be produced or whether the default segment register DS is used. The second (DI) operand must be addressible from the ES register; no segment override is possible.

After the comparison is made, both SI and DI are automatically advanced. If the direction flag is 0 (CLD was executed), the registers increment; if the direction flag is 1 (STD was executed), the regis- ters decrement. The registers increment or decrement by 1 if a byte was moved; by 2 if a word was moved.

CMPS can be preceded by the REPE or REPNE prefix for block comparison of CX bytes or words. Refer to the REP instruction for details of this operation.

PROTECTED MODE EXCEPTIONS

#GP(O) for an illegal memory operand effective address in the CS, DS, or ES segments; #SS(O) for an illegal address in the SS segment.

REAL ADDRESS MODE EXCEPTIONS

Tntf"rrl1,.,t 11 fnr ~ wnrn ()np.r~ nn "t ()ff~p.t OFFFFH. | |