Register Description

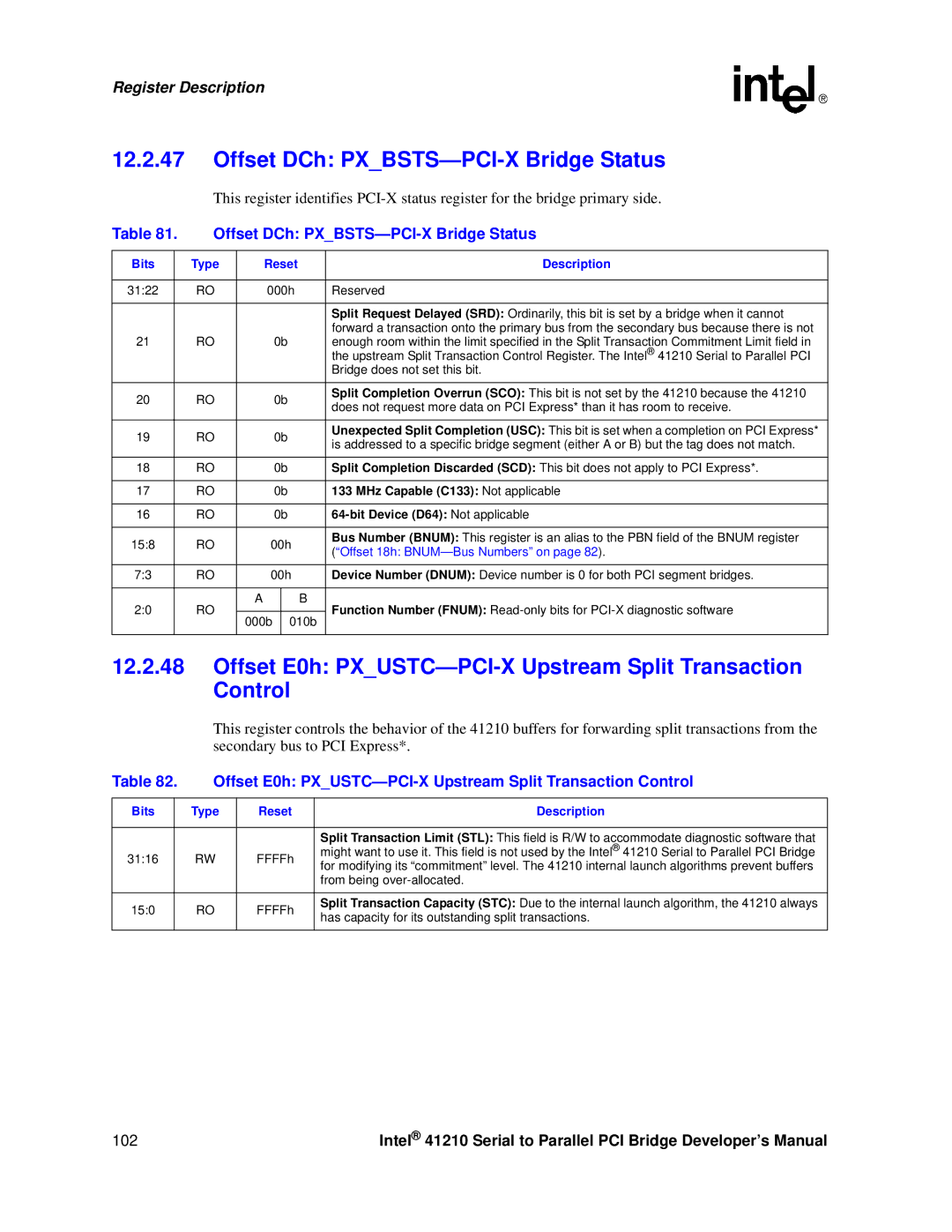

12.2.47Offset DCh: PX_BSTS—PCI-X Bridge Status

This register identifies

Table 81. | Offset DCh: | ||||||

|

|

|

|

|

|

| |

Bits |

| Type |

| Reset | Description | ||

|

|

|

|

|

| ||

31:22 |

| RO |

| 000h | Reserved | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Split Request Delayed (SRD): Ordinarily, this bit is set by a bridge when it cannot |

21 |

| RO |

|

| 0b | forward a transaction onto the primary bus from the secondary bus because there is not | |

|

|

| enough room within the limit specified in the Split Transaction Commitment Limit field in | ||||

|

|

|

|

|

|

| the upstream Split Transaction Control Register. The Intel® 41210 Serial to Parallel PCI |

|

|

|

|

|

|

| Bridge does not set this bit. |

|

|

|

|

|

|

|

|

20 |

| RO |

|

| 0b | Split Completion Overrun (SCO): This bit is not set by the 41210 because the 41210 | |

|

|

| does not request more data on PCI Express* than it has room to receive. | ||||

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

19 |

| RO |

|

| 0b | Unexpected Split Completion (USC): This bit is set when a completion on PCI Express* | |

|

|

| is addressed to a specific bridge segment (either A or B) but the tag does not match. | ||||

|

|

|

|

|

|

| |

|

|

|

|

|

|

| |

18 |

| RO |

|

| 0b | Split Completion Discarded (SCD): This bit does not apply to PCI Express*. | |

|

|

|

|

|

|

| |

17 |

| RO |

|

| 0b | 133 MHz Capable (C133): Not applicable | |

|

|

|

|

|

|

| |

16 |

| RO |

|

| 0b |

| |

|

|

|

|

|

|

|

|

15:8 |

| RO |

| 00h | Bus Number (BNUM): This register is an alias to the PBN field of the BNUM register | ||

|

| (“Offset 18h: | |||||

|

|

|

|

|

|

| |

|

|

|

|

|

| ||

7:3 |

| RO |

| 00h | Device Number (DNUM): Device number is 0 for both PCI segment bridges. | ||

|

|

|

|

|

|

|

|

2:0 |

| RO | A |

|

| B | Function Number (FNUM): |

|

|

|

|

| |||

| 000b |

| 010b | ||||

|

|

|

|

| |||

|

|

|

|

|

|

|

|

12.2.48Offset E0h: PX_USTC—PCI-X Upstream Split Transaction Control

This register controls the behavior of the 41210 buffers for forwarding split transactions from the secondary bus to PCI Express*.

Table 82. | Offset E0h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

|

|

|

| Split Transaction Limit (STL): This field is R/W to accommodate diagnostic software that |

31:16 |

| RW | FFFFh | might want to use it. This field is not used by the Intel® 41210 Serial to Parallel PCI Bridge |

| for modifying its “commitment” level. The 41210 internal launch algorithms prevent buffers | |||

|

|

|

| |

|

|

|

| from being |

|

|

|

|

|

15:0 |

| RO | FFFFh | Split Transaction Capacity (STC): Due to the internal launch algorithm, the 41210 always |

| has capacity for its outstanding split transactions. | |||

|

|

|

| |

|

|

|

|

|

102 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |