Register Description

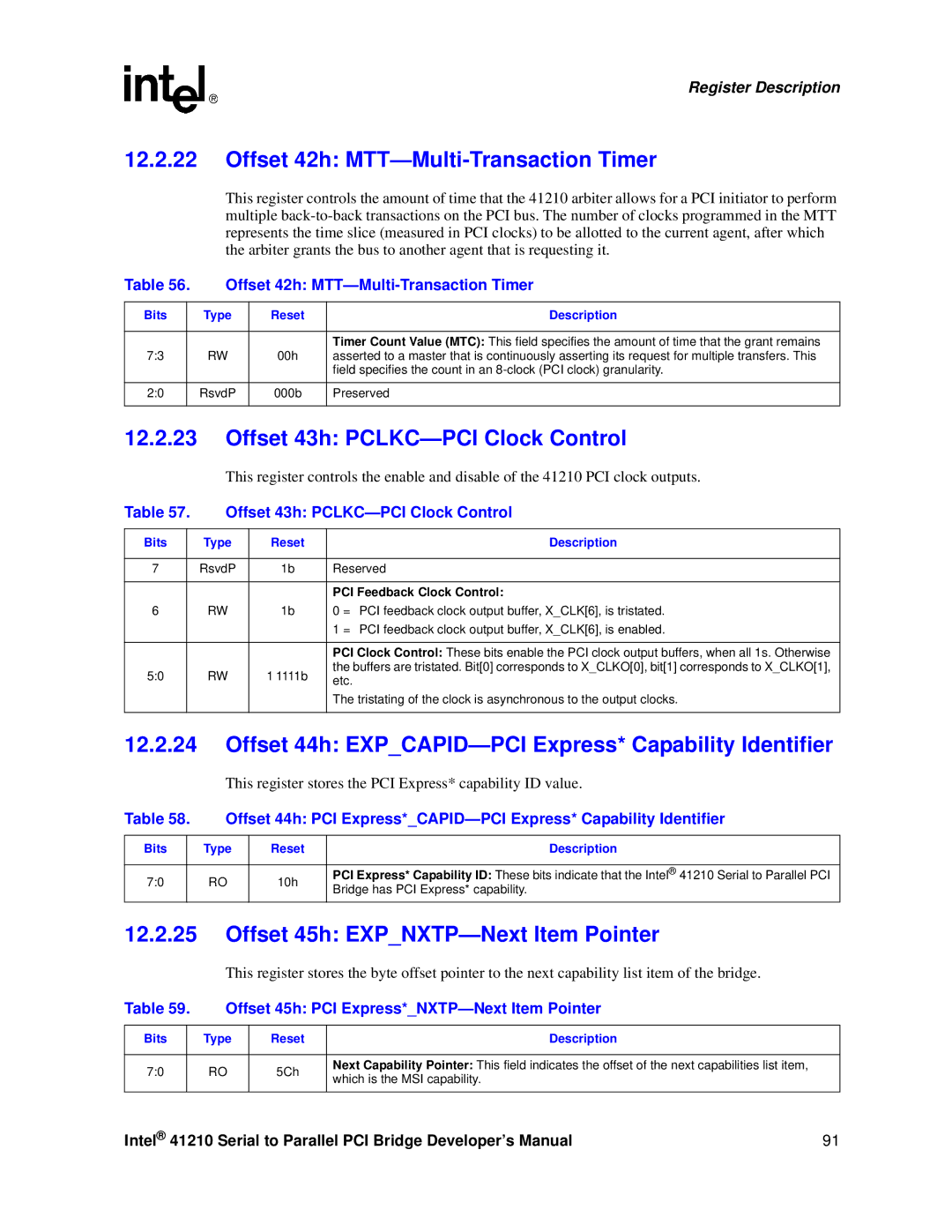

12.2.22Offset 42h: MTT—Multi-Transaction Timer

This register controls the amount of time that the 41210 arbiter allows for a PCI initiator to perform multiple

Table 56. | Offset 42h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

7:3 |

| RW | 00h | Timer Count Value (MTC): This field specifies the amount of time that the grant remains |

| asserted to a master that is continuously asserting its request for multiple transfers. This | |||

|

|

|

| field specifies the count in an |

|

|

|

|

|

2:0 |

| RsvdP | 000b | Preserved |

|

|

|

|

|

12.2.23Offset 43h: PCLKC—PCI Clock Control

This register controls the enable and disable of the 41210 PCI clock outputs.

Table 57. | Offset 43h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

7 |

| RsvdP | 1b | Reserved |

|

|

|

|

|

|

|

|

| PCI Feedback Clock Control: |

6 |

| RW | 1b | 0 = PCI feedback clock output buffer, X_CLK[6], is tristated. |

|

|

|

| 1 = PCI feedback clock output buffer, X_CLK[6], is enabled. |

|

|

|

|

|

|

|

|

| PCI Clock Control: These bits enable the PCI clock output buffers, when all 1s. Otherwise |

5:0 |

| RW | 1 1111b | the buffers are tristated. Bit[0] corresponds to X_CLKO[0], bit[1] corresponds to X_CLKO[1], |

| etc. | |||

|

|

|

| |

|

|

|

| The tristating of the clock is asynchronous to the output clocks. |

|

|

|

|

|

12.2.24Offset 44h: EXP_CAPID—PCI Express* Capability Identifier

This register stores the PCI Express* capability ID value.

Table 58. Offset 44h: PCI

Bits | Type | Reset | Description | |

|

|

|

| |

7:0 | RO | 10h | PCI Express* Capability ID: These bits indicate that the Intel® 41210 Serial to Parallel PCI | |

Bridge has PCI Express* capability. | ||||

|

|

| ||

|

|

|

|

12.2.25Offset 45h: EXP_NXTP—Next Item Pointer

This register stores the byte offset pointer to the next capability list item of the bridge.

Table 59. | Offset 45h: PCI | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

7:0 |

| RO | 5Ch | Next Capability Pointer: This field indicates the offset of the next capabilities list item, |

| which is the MSI capability. | |||

|

|

|

| |

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 91 |