Error Handling

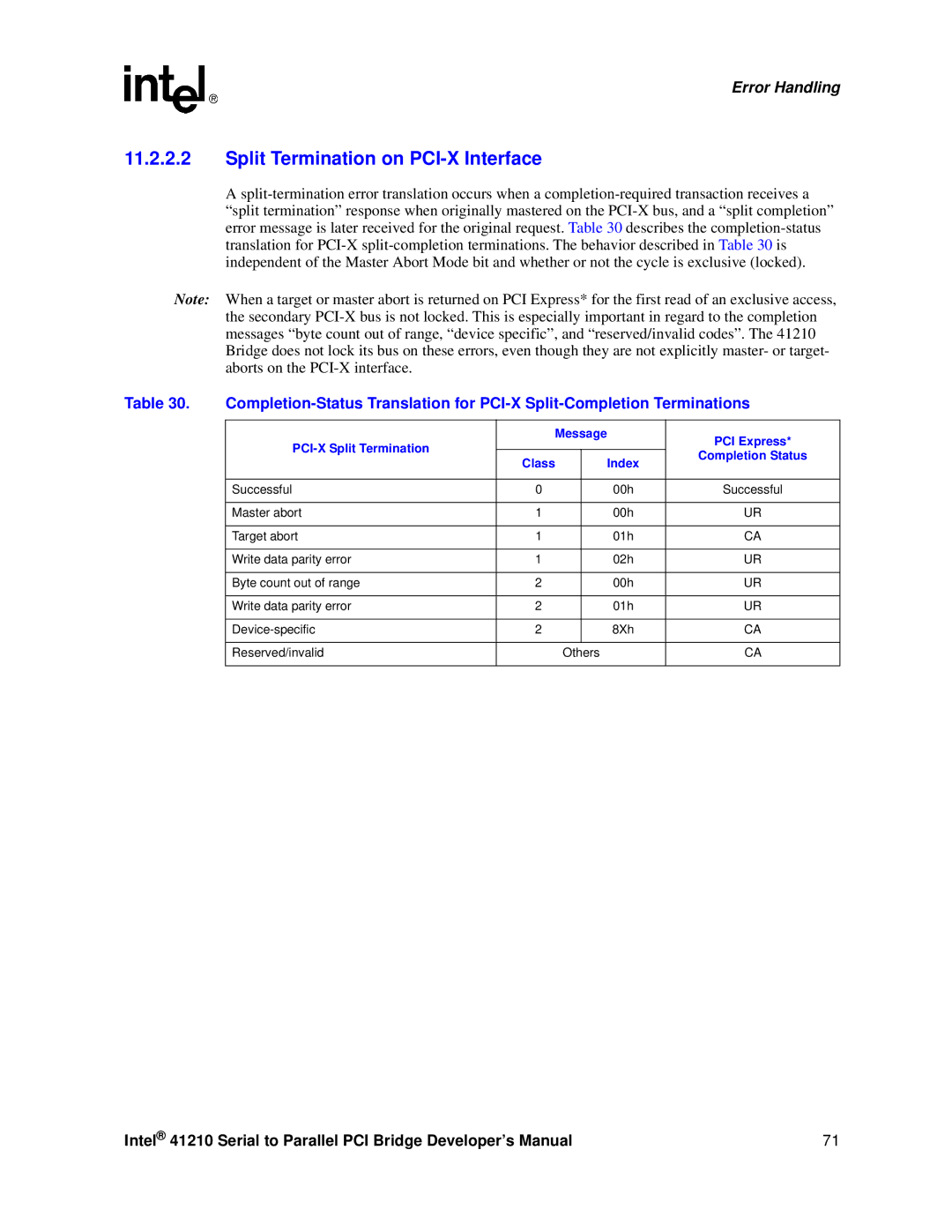

11.2.2.2Split Termination on PCI-X Interface

A

Note: When a target or master abort is returned on PCI Express* for the first read of an exclusive access, the secondary

Table 30.

| Message | PCI Express* | ||

|

|

| ||

|

|

| Completion Status | |

Class |

| Index | ||

|

| |||

|

|

| ||

|

|

|

|

|

Successful | 0 |

| 00h | Successful |

|

|

|

|

|

Master abort | 1 |

| 00h | UR |

|

|

|

|

|

Target abort | 1 |

| 01h | CA |

|

|

|

|

|

Write data parity error | 1 |

| 02h | UR |

|

|

|

|

|

Byte count out of range | 2 |

| 00h | UR |

|

|

|

|

|

Write data parity error | 2 |

| 01h | UR |

|

|

|

|

|

2 |

| 8Xh | CA | |

|

|

|

|

|

Reserved/invalid |

| Others | CA | |

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 71 |