Register Description

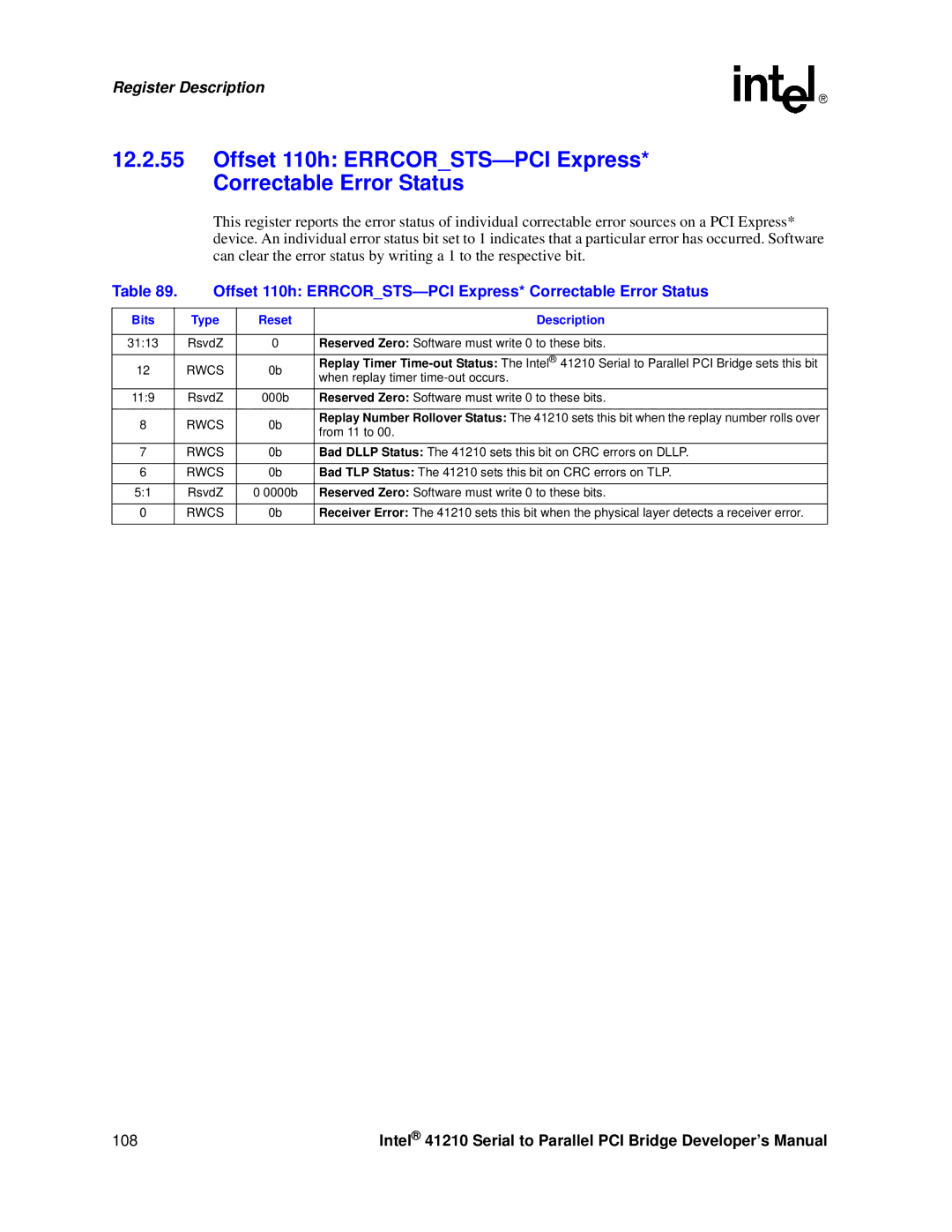

12.2.55Offset 110h: ERRCOR_STS—PCI Express* Correctable Error Status

This register reports the error status of individual correctable error sources on a PCI Express* device. An individual error status bit set to 1 indicates that a particular error has occurred. Software can clear the error status by writing a 1 to the respective bit.

Table 89. | Offset 110h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

31:13 |

| RsvdZ | 0 | Reserved Zero: Software must write 0 to these bits. |

|

|

|

|

|

12 |

| RWCS | 0b | Replay Timer |

| when replay timer | |||

|

|

|

| |

11:9 |

| RsvdZ | 000b | Reserved Zero: Software must write 0 to these bits. |

|

|

|

|

|

8 |

| RWCS | 0b | Replay Number Rollover Status: The 41210 sets this bit when the replay number rolls over |

| from 11 to 00. | |||

|

|

|

| |

7 |

| RWCS | 0b | Bad DLLP Status: The 41210 sets this bit on CRC errors on DLLP. |

|

|

|

|

|

6 |

| RWCS | 0b | Bad TLP Status: The 41210 sets this bit on CRC errors on TLP. |

|

|

|

|

|

5:1 |

| RsvdZ | 0 0000b | Reserved Zero: Software must write 0 to these bits. |

|

|

|

|

|

0 |

| RWCS | 0b | Receiver Error: The 41210 sets this bit when the physical layer detects a receiver error. |

|

|

|

|

|

108 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |