Register Description

12.2.51Offset 100h:

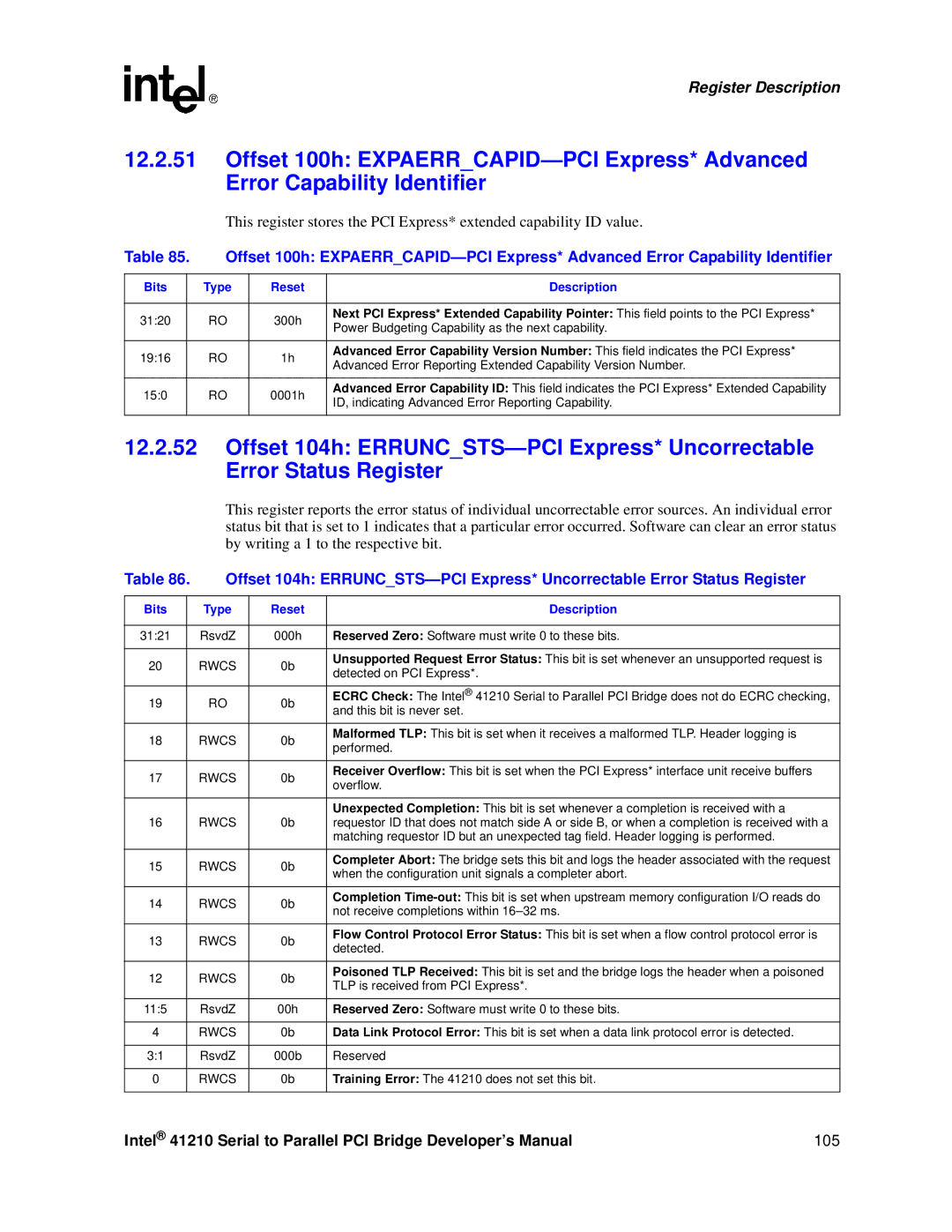

This register stores the PCI Express* extended capability ID value.

Table 85. | Offset 100h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

31:20 |

| RO | 300h | Next PCI Express* Extended Capability Pointer: This field points to the PCI Express* |

| Power Budgeting Capability as the next capability. | |||

|

|

|

| |

|

|

|

|

|

19:16 |

| RO | 1h | Advanced Error Capability Version Number: This field indicates the PCI Express* |

| Advanced Error Reporting Extended Capability Version Number. | |||

|

|

|

| |

|

|

|

|

|

15:0 |

| RO | 0001h | Advanced Error Capability ID: This field indicates the PCI Express* Extended Capability |

| ID, indicating Advanced Error Reporting Capability. | |||

|

|

|

| |

|

|

|

|

|

12.2.52Offset 104h:

This register reports the error status of individual uncorrectable error sources. An individual error status bit that is set to 1 indicates that a particular error occurred. Software can clear an error status by writing a 1 to the respective bit.

Table 86. | Offset 104h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

31:21 |

| RsvdZ | 000h | Reserved Zero: Software must write 0 to these bits. |

|

|

|

|

|

20 |

| RWCS | 0b | Unsupported Request Error Status: This bit is set whenever an unsupported request is |

| detected on PCI Express*. | |||

|

|

|

| |

|

|

|

|

|

19 |

| RO | 0b | ECRC Check: The Intel® 41210 Serial to Parallel PCI Bridge does not do ECRC checking, |

| and this bit is never set. | |||

|

|

|

| |

|

|

|

|

|

18 |

| RWCS | 0b | Malformed TLP: This bit is set when it receives a malformed TLP. Header logging is |

| performed. | |||

|

|

|

| |

|

|

|

|

|

17 |

| RWCS | 0b | Receiver Overflow: This bit is set when the PCI Express* interface unit receive buffers |

| overflow. | |||

|

|

|

| |

|

|

|

|

|

|

|

|

| Unexpected Completion: This bit is set whenever a completion is received with a |

16 |

| RWCS | 0b | requestor ID that does not match side A or side B, or when a completion is received with a |

|

|

|

| matching requestor ID but an unexpected tag field. Header logging is performed. |

|

|

|

|

|

15 |

| RWCS | 0b | Completer Abort: The bridge sets this bit and logs the header associated with the request |

| when the configuration unit signals a completer abort. | |||

|

|

|

| |

|

|

|

|

|

14 |

| RWCS | 0b | Completion |

| not receive completions within | |||

|

|

|

| |

|

|

|

|

|

13 |

| RWCS | 0b | Flow Control Protocol Error Status: This bit is set when a flow control protocol error is |

| detected. | |||

|

|

|

| |

|

|

|

|

|

12 |

| RWCS | 0b | Poisoned TLP Received: This bit is set and the bridge logs the header when a poisoned |

| TLP is received from PCI Express*. | |||

|

|

|

| |

|

|

|

|

|

11:5 |

| RsvdZ | 00h | Reserved Zero: Software must write 0 to these bits. |

|

|

|

|

|

4 |

| RWCS | 0b | Data Link Protocol Error: This bit is set when a data link protocol error is detected. |

|

|

|

|

|

3:1 |

| RsvdZ | 000b | Reserved |

|

|

|

|

|

0 |

| RWCS | 0b | Training Error: The 41210 does not set this bit. |

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 105 |