| Contents | |

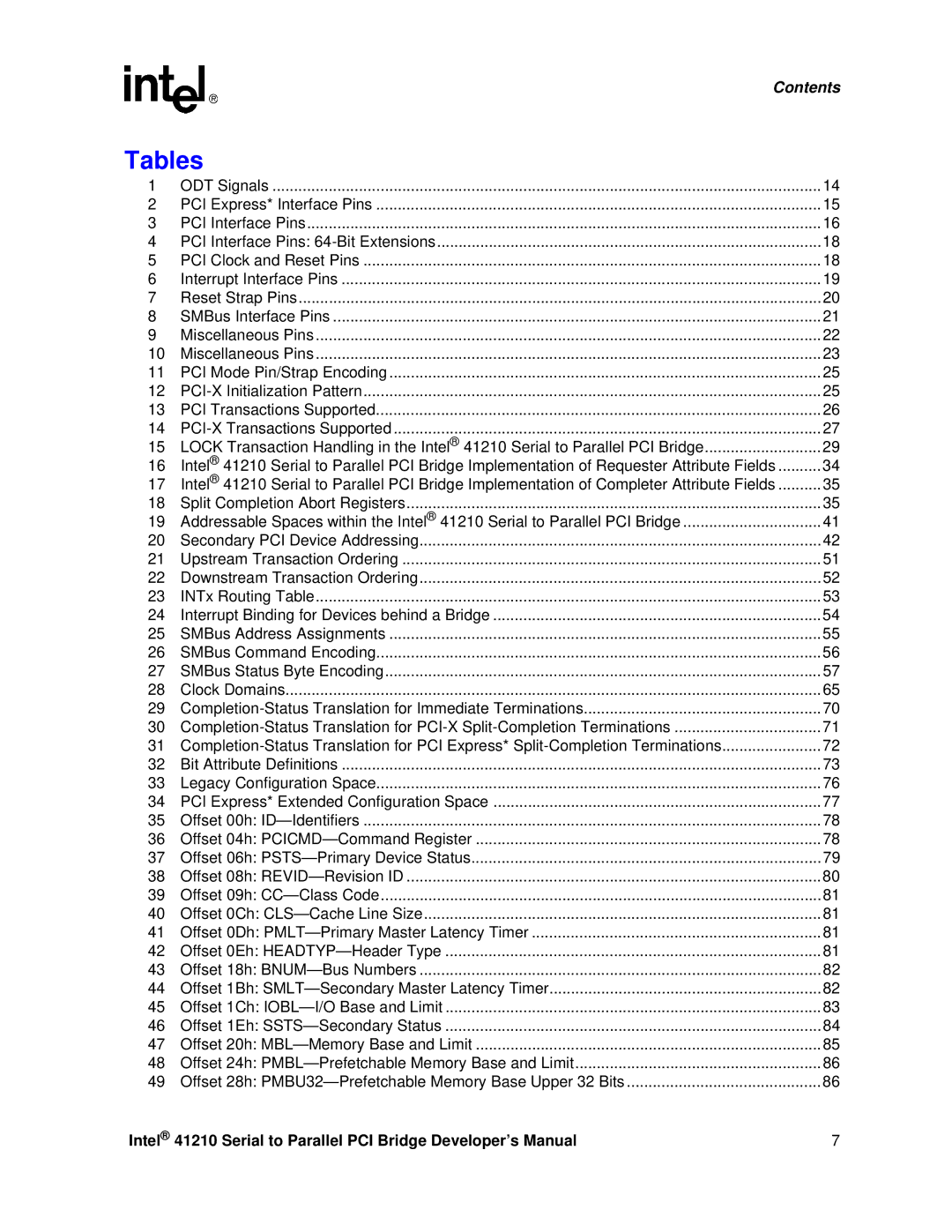

Tables |

| |

1 | ODT Signals | 14 |

2 | PCI Express* Interface Pins | 15 |

3 | PCI Interface Pins | 16 |

4 | PCI Interface Pins: | 18 |

5 | PCI Clock and Reset Pins | 18 |

6 | Interrupt Interface Pins | 19 |

7 | Reset Strap Pins | 20 |

8 | SMBus Interface Pins | 21 |

9 | Miscellaneous Pins | 22 |

10 | Miscellaneous Pins | 23 |

11 | PCI Mode Pin/Strap Encoding | 25 |

12 | 25 | |

13 | PCI Transactions Supported | 26 |

14 | 27 | |

15 | LOCK Transaction Handling in the Intel® 41210 Serial to Parallel PCI Bridge | 29 |

16 | Intel® 41210 Serial to Parallel PCI Bridge Implementation of Requester Attribute Fields | 34 |

17 | Intel® 41210 Serial to Parallel PCI Bridge Implementation of Completer Attribute Fields | 35 |

18 | Split Completion Abort Registers | 35 |

19 | Addressable Spaces within the Intel® 41210 Serial to Parallel PCI Bridge | 41 |

20 | Secondary PCI Device Addressing | 42 |

21 | Upstream Transaction Ordering | 51 |

22 | Downstream Transaction Ordering | 52 |

23 | INTx Routing Table | 53 |

24 | Interrupt Binding for Devices behind a Bridge | 54 |

25 | SMBus Address Assignments | 55 |

26 | SMBus Command Encoding | 56 |

27 | SMBus Status Byte Encoding | 57 |

28 | Clock Domains | 65 |

29 | 70 | |

30 | 71 | |

31 | 72 | |

32 | Bit Attribute Definitions | 73 |

33 | Legacy Configuration Space | 76 |

34 | PCI Express* Extended Configuration Space | 77 |

35 | Offset 00h: | 78 |

36 | Offset 04h: | 78 |

37 | Offset 06h: | 79 |

38 | Offset 08h: | 80 |

39 | Offset 09h: | 81 |

40 | Offset 0Ch: | 81 |

41 | Offset 0Dh: | 81 |

42 | Offset 0Eh: | 81 |

43 | Offset 18h: | 82 |

44 | Offset 1Bh: | 82 |

45 | Offset 1Ch: | 83 |

46 | Offset 1Eh: | 84 |

47 | Offset 20h: | 85 |

48 | Offset 24h: | 86 |

49 | Offset 28h: | 86 |

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 7 | |