Register Description

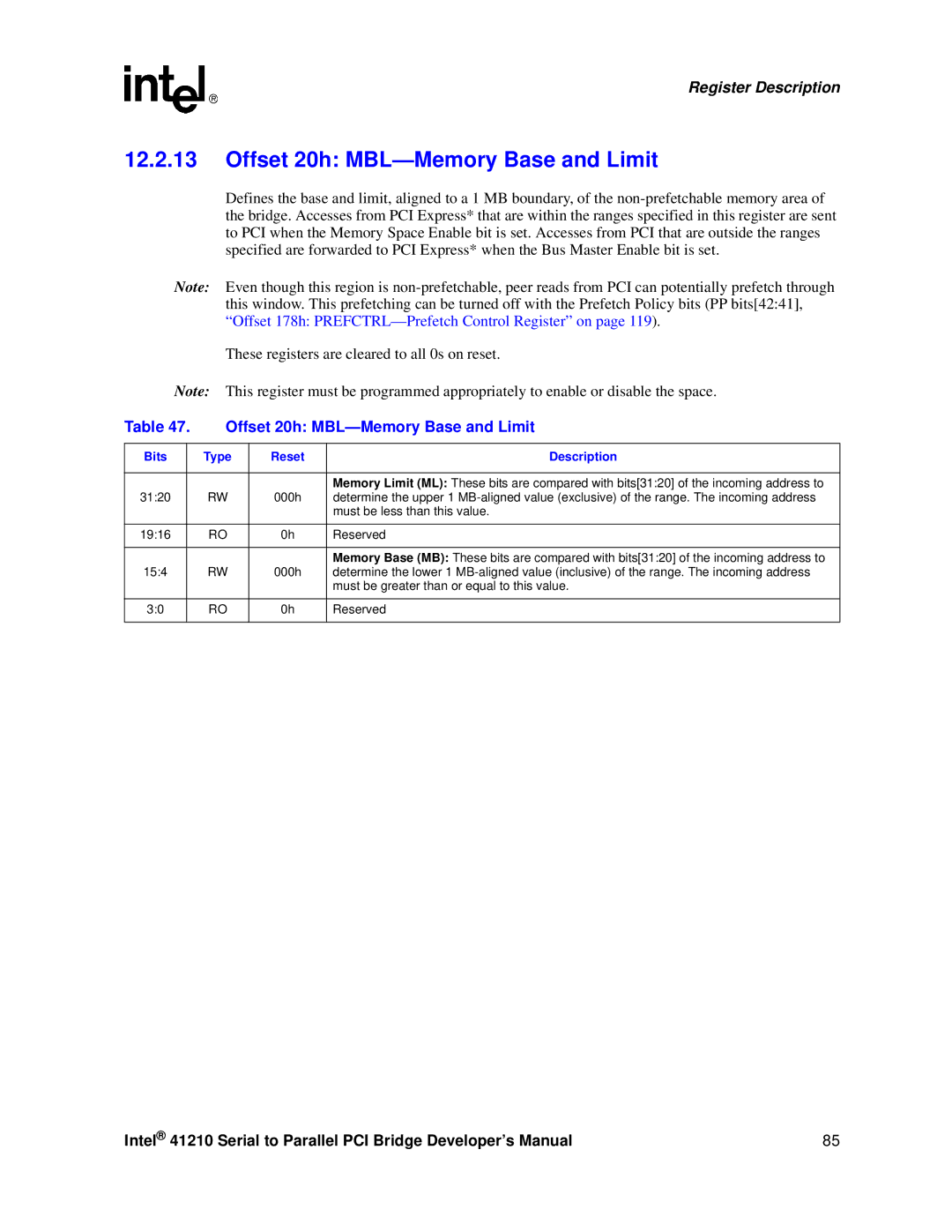

12.2.13Offset 20h: MBL—Memory Base and Limit

Defines the base and limit, aligned to a 1 MB boundary, of the

Note: Even though this region is

These registers are cleared to all 0s on reset.

Note: This register must be programmed appropriately to enable or disable the space.

Table 47. | Offset 20h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

31:20 |

| RW | 000h | Memory Limit (ML): These bits are compared with bits[31:20] of the incoming address to |

| determine the upper 1 | |||

|

|

|

| must be less than this value. |

|

|

|

|

|

19:16 |

| RO | 0h | Reserved |

|

|

|

|

|

|

|

|

| Memory Base (MB): These bits are compared with bits[31:20] of the incoming address to |

15:4 |

| RW | 000h | determine the lower 1 |

|

|

|

| must be greater than or equal to this value. |

|

|

|

|

|

3:0 |

| RO | 0h | Reserved |

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 85 |