3.2.5LOCK Cycles

A lock is established when all the following conditions are true:

•A PCI Express* device initiates a Memory Read Lock (MRdLk) request to read from a target PCI device.

•LOCK# is asserted on the PCI bus.

•The target PCI device responds with a TRDY#.

The bus is unlocked when the Unlock Message is received on PCI Express*.

When the PCI bus is locked, all upstream memory transactions from that bus are retried. The 41210 upstream read prefetch engine stops issuing any more requests on the PCI Express* bus. However, note that the 41210 accepts read completions for upstream read requests that were issued before the lock was established on the PCI bus when they return on PCI Express*.

As soon as the bus is locked, any PCI Express* cycle to PCI is driven with the LOCK# pin asserted, even when that particular cycle is not locked. This is not expected to occur, because under lock,

When one PCI bus segment is locked, the other is still free to accept cycles (in other words, that bus is not locked. However, these transactions are not allowed to proceed on PCI Express* or the locked PCI segment). Therefore, as soon as the PCI bus is locked, additional cycles do not proceed onto PCI Express* from the

During the LOCK sequence, when the initial locked read command results in a master or target abort (either on the PCI bus or the internal switch interconnect), the 41210 does not establish lock, and it sends a completion packet on PCI Express* with an error status. In case of a subsequent memory read or memory write receiving a target or master abort during a LOCK sequence, the 41210 unlocks only after the unlock message is received on PCI Express*.

•Downstream LOCK is supported by the 41210.

•Upstream LOCK transactions are treated with the LOCK signal ignored.

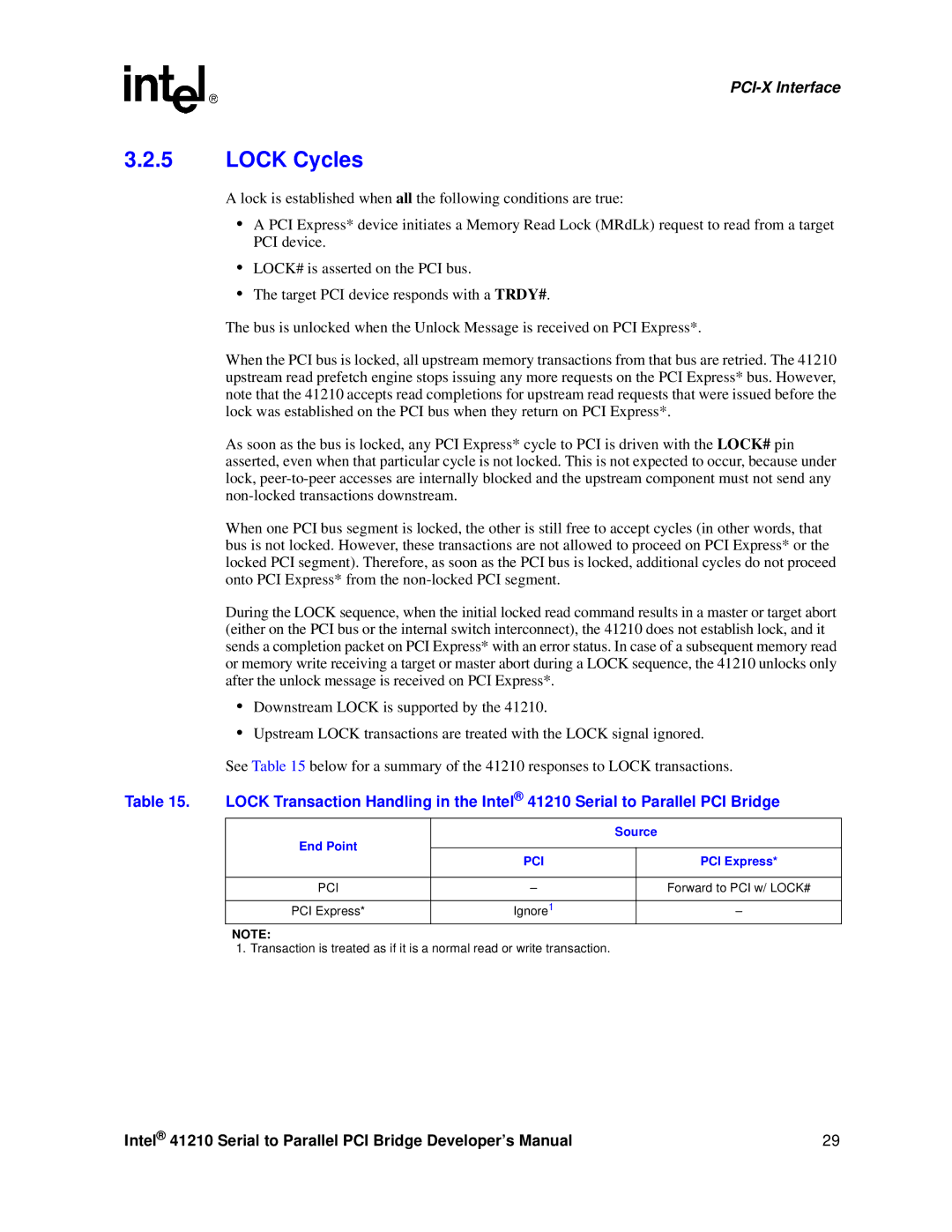

See Table 15 below for a summary of the 41210 responses to LOCK transactions.

Table 15. LOCK Transaction Handling in the Intel® 41210 Serial to Parallel PCI Bridge

End Point |

| Source | |

|

|

| |

PCI |

| PCI Express* | |

|

| ||

|

|

|

|

PCI | – |

| Forward to PCI w/ LOCK# |

|

|

|

|

PCI Express* | Ignore1 |

| – |

NOTE: |

|

|

|

1. Transaction is treated as if it is a normal read or write transaction.

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 29 |