Register Description

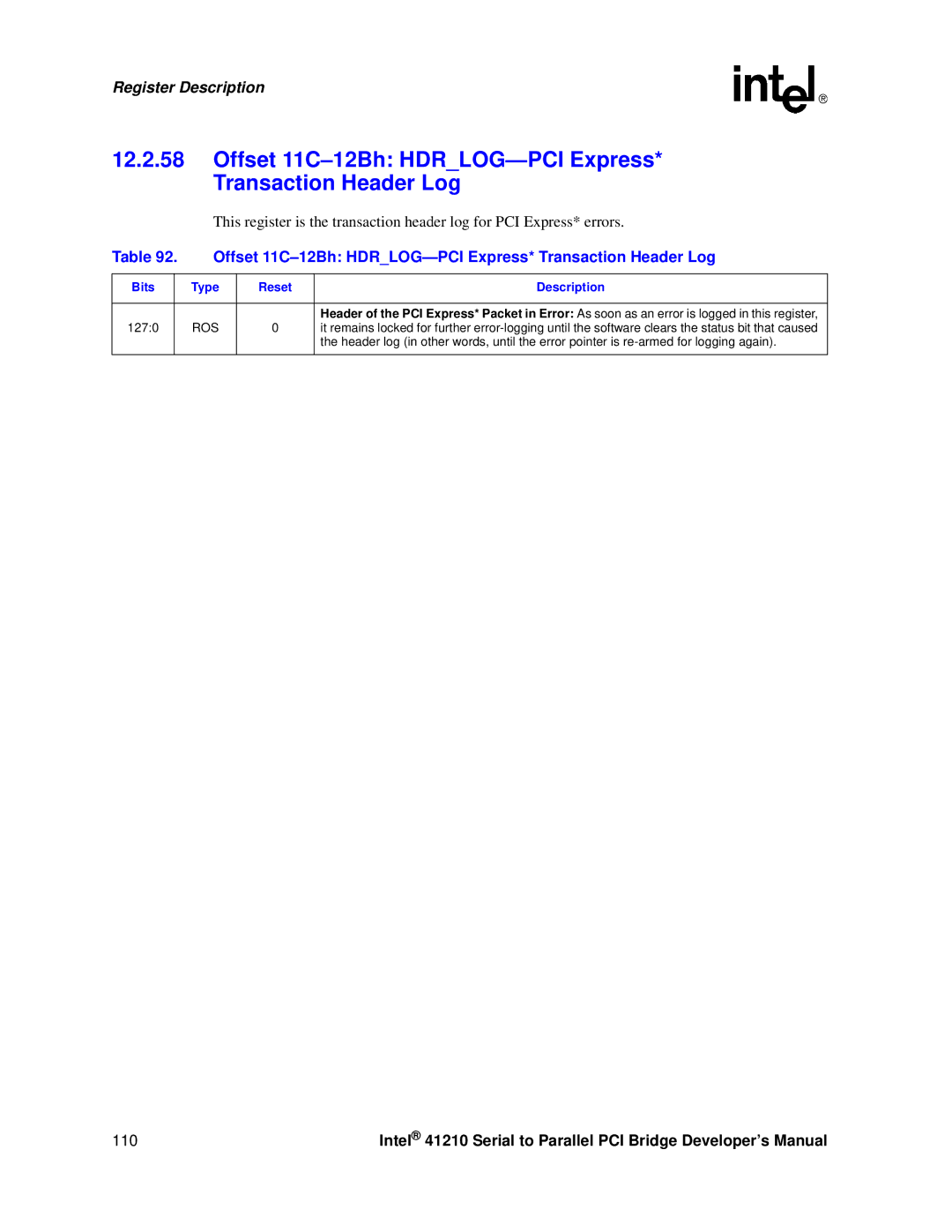

12.2.58Offset 11C–12Bh: HDR_LOG—PCI Express* Transaction Header Log

This register is the transaction header log for PCI Express* errors.

Table 92. | Offset | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

127:0 |

| ROS | 0 | Header of the PCI Express* Packet in Error: As soon as an error is logged in this register, |

| it remains locked for further | |||

|

|

|

| the header log (in other words, until the error pointer is |

|

|

|

|

|

110 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |