Register Description

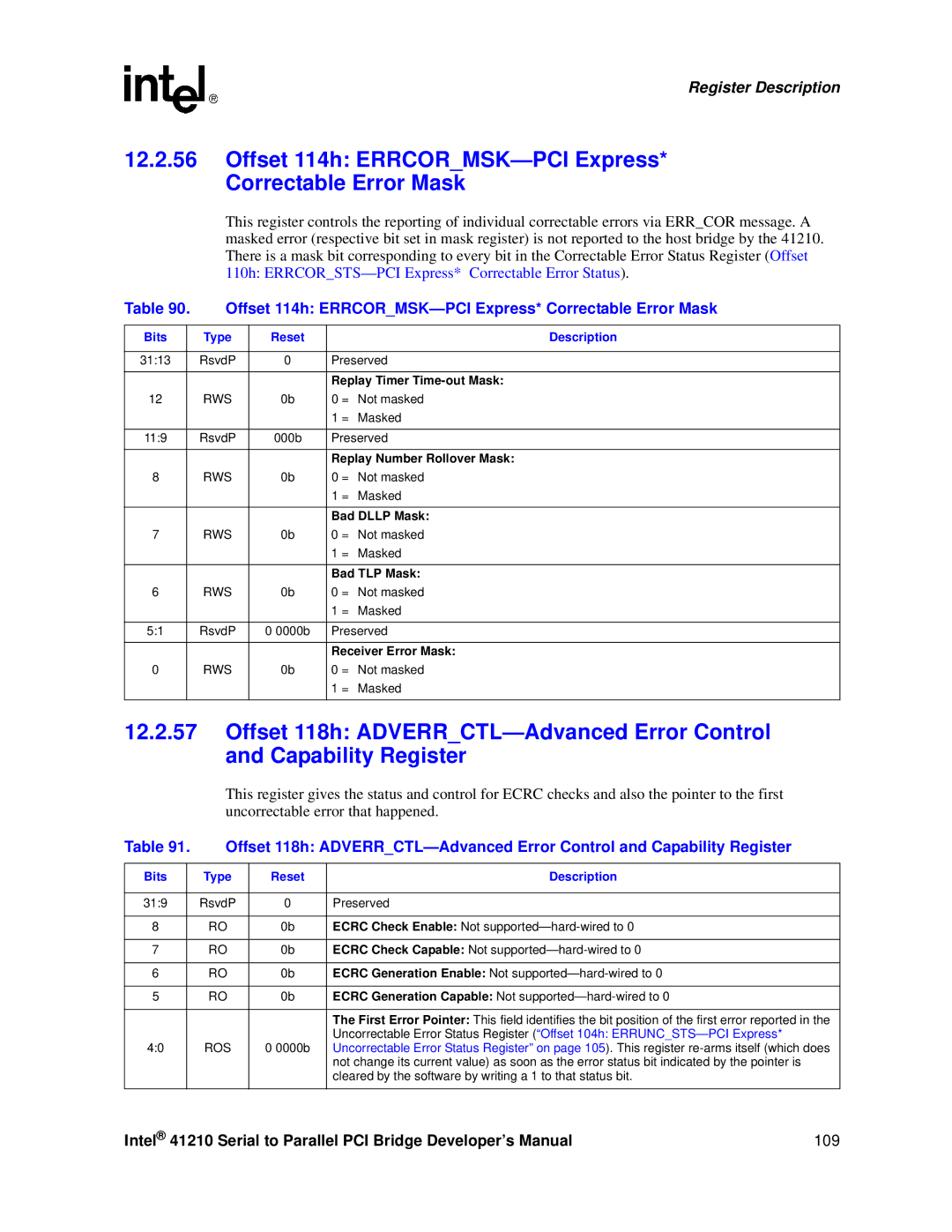

12.2.56Offset 114h: ERRCOR_MSK—PCI Express* Correctable Error Mask

This register controls the reporting of individual correctable errors via ERR_COR message. A masked error (respective bit set in mask register) is not reported to the host bridge by the 41210. There is a mask bit corresponding to every bit in the Correctable Error Status Register (Offset 110h:

Table 90. | Offset 114h: | ||||

|

|

|

|

|

|

Bits |

| Type | Reset |

| Description |

|

|

|

|

| |

31:13 |

| RsvdP | 0 | Preserved | |

|

|

|

|

| |

|

|

|

| Replay Timer | |

12 |

| RWS | 0b | 0 = | Not masked |

|

|

|

| 1 = | Masked |

|

|

|

|

| |

11:9 |

| RsvdP | 000b | Preserved | |

|

|

|

|

| |

|

|

|

| Replay Number Rollover Mask: | |

8 |

| RWS | 0b | 0 = | Not masked |

|

|

|

| 1 = | Masked |

|

|

|

|

| |

|

|

|

| Bad DLLP Mask: | |

7 |

| RWS | 0b | 0 = | Not masked |

|

|

|

| 1 = | Masked |

|

|

|

|

| |

|

|

|

| Bad TLP Mask: | |

6 |

| RWS | 0b | 0 = | Not masked |

|

|

|

| 1 = | Masked |

|

|

|

|

| |

5:1 |

| RsvdP | 0 0000b | Preserved | |

|

|

|

|

| |

|

|

|

| Receiver Error Mask: | |

0 |

| RWS | 0b | 0 = | Not masked |

|

|

|

| 1 = | Masked |

|

|

|

|

|

|

12.2.57Offset 118h:

This register gives the status and control for ECRC checks and also the pointer to the first uncorrectable error that happened.

Table 91. | Offset 118h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

31:9 |

| RsvdP | 0 | Preserved |

|

|

|

|

|

8 |

| RO | 0b | ECRC Check Enable: Not |

|

|

|

|

|

7 |

| RO | 0b | ECRC Check Capable: Not |

|

|

|

|

|

6 |

| RO | 0b | ECRC Generation Enable: Not |

|

|

|

|

|

5 |

| RO | 0b | ECRC Generation Capable: Not |

|

|

|

|

|

|

|

|

| The First Error Pointer: This field identifies the bit position of the first error reported in the |

4:0 |

| ROS | 0 0000b | Uncorrectable Error Status Register (“Offset 104h: |

| Uncorrectable Error Status Register” on page 105). This register | |||

|

|

|

| not change its current value) as soon as the error status bit indicated by the pointer is |

|

|

|

| cleared by the software by writing a 1 to that status bit. |

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 109 |