Register Description

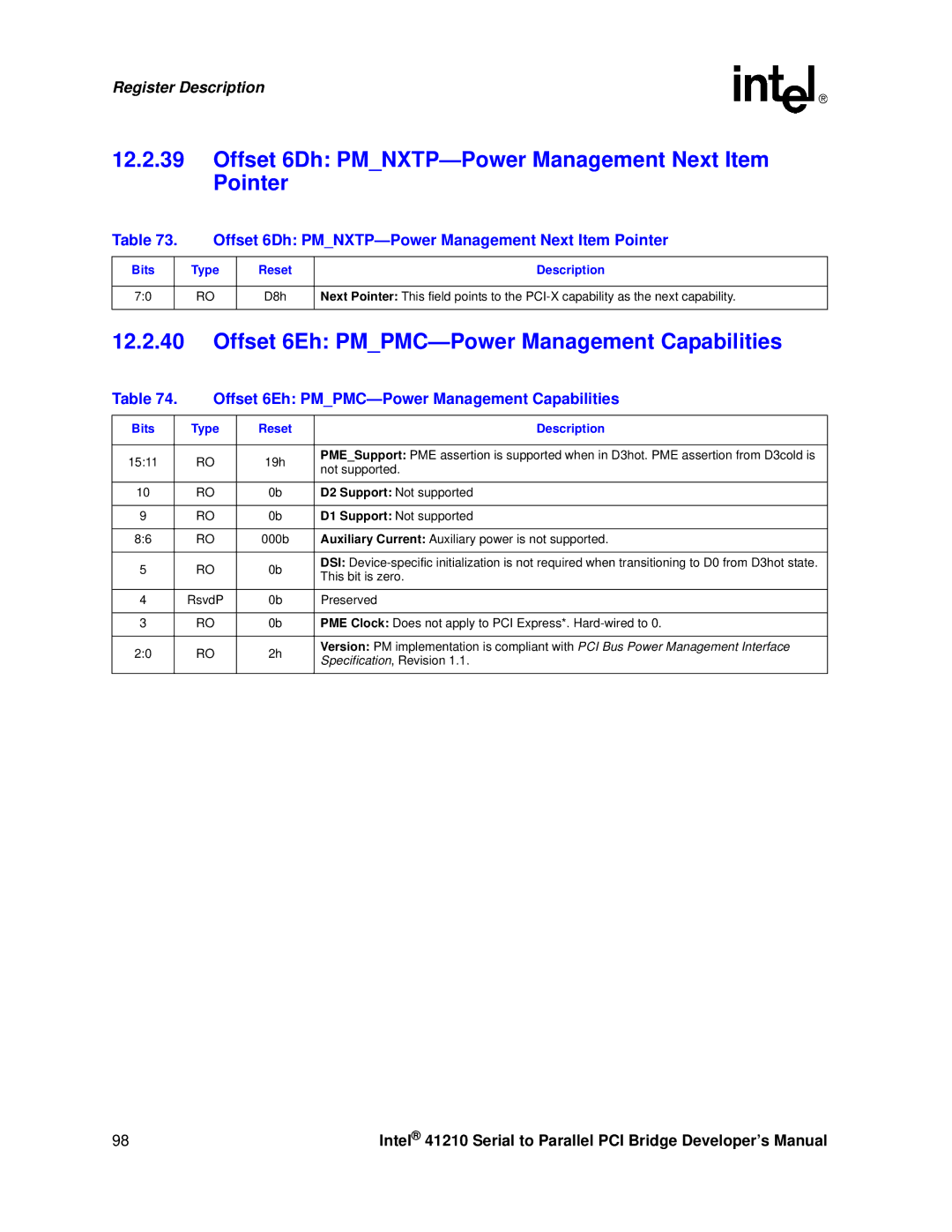

12.2.39Offset 6Dh: PM_NXTP—Power Management Next Item Pointer

Table 73. | Offset 6Dh: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

7:0 |

| RO | D8h | Next Pointer: This field points to the |

|

|

|

|

|

12.2.40Offset 6Eh: PM_PMC—Power Management Capabilities

Table 74. | Offset 6Eh: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

15:11 |

| RO | 19h | PME_Support: PME assertion is supported when in D3hot. PME assertion from D3cold is |

| not supported. | |||

|

|

|

| |

|

|

|

|

|

10 |

| RO | 0b | D2 Support: Not supported |

|

|

|

|

|

9 |

| RO | 0b | D1 Support: Not supported |

|

|

|

|

|

8:6 |

| RO | 000b | Auxiliary Current: Auxiliary power is not supported. |

|

|

|

|

|

5 |

| RO | 0b | DSI: |

| This bit is zero. | |||

|

|

|

| |

|

|

|

|

|

4 |

| RsvdP | 0b | Preserved |

|

|

|

|

|

3 |

| RO | 0b | PME Clock: Does not apply to PCI Express*. |

|

|

|

|

|

2:0 |

| RO | 2h | Version: PM implementation is compliant with PCI Bus Power Management Interface |

| Specification, Revision 1.1. | |||

|

|

|

| |

|

|

|

|

|

98 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |