|

|

|

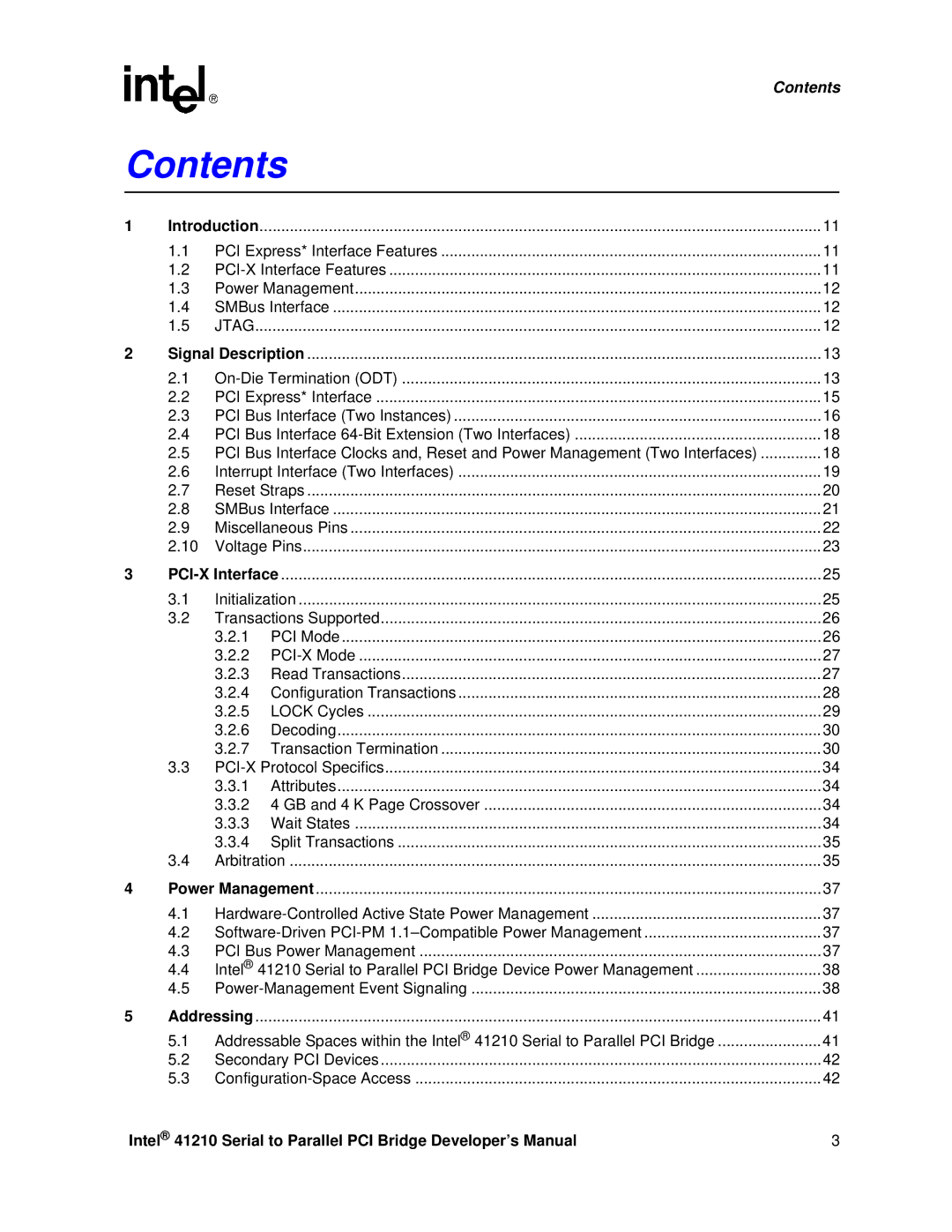

| Contents |

Contents |

| |||

1 | Introduction | .................................................................................................................................. | 11 | |

| 1.1 | PCI Express* Interface Features | 11 | |

| 1.2 | 11 | ||

| 1.3 | Power Management | 12 | |

| 1.4 | SMBus Interface | 12 | |

| 1.5 | JTAG | 12 | |

2 | Signal Description | 13 | ||

| 2.1 | 13 | ||

| 2.2 | PCI Express* Interface | 15 | |

| 2.3 | PCI Bus Interface (Two Instances) | 16 | |

| 2.4 | PCI Bus Interface | 18 | |

| 2.5 | PCI Bus Interface Clocks and, Reset and Power Management (Two Interfaces) | 18 | |

| 2.6 | Interrupt Interface (Two Interfaces) | 19 | |

| 2.7 | Reset Straps | 20 | |

| 2.8 | SMBus Interface | 21 | |

| 2.9 | Miscellaneous Pins | 22 | |

| 2.10 | Voltage Pins | 23 | |

3 | 25 | |||

| 3.1 | Initialization | 25 | |

| 3.2 | Transactions Supported | 26 | |

|

| 3.2.1 | PCI Mode | 26 |

|

| 3.2.2 | 27 | |

|

| 3.2.3 | Read Transactions | 27 |

|

| 3.2.4 | Configuration Transactions | 28 |

|

| 3.2.5 | LOCK Cycles | 29 |

|

| 3.2.6 | Decoding | 30 |

|

| 3.2.7 | Transaction Termination | 30 |

| 3.3 | 34 | ||

|

| 3.3.1 | Attributes | 34 |

|

| 3.3.2 4 GB and 4 K Page Crossover | 34 | |

|

| 3.3.3 | Wait States | 34 |

|

| 3.3.4 | Split Transactions | 35 |

| 3.4 | Arbitration | 35 | |

4 | Power Management | 37 | ||

| 4.1 | 37 | ||

| 4.2 | 37 | ||

| 4.3 | PCI Bus Power Management | 37 | |

| 4.4 | Intel® 41210 Serial to Parallel PCI Bridge Device Power Management | 38 | |

| 4.5 | 38 | ||

5 | Addressing | 41 | ||

| 5.1 | Addressable Spaces within the Intel® 41210 Serial to Parallel PCI Bridge | 41 | |

| 5.2 | Secondary PCI Devices | 42 | |

| 5.3 | 42 | ||

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 3 |