Addressing

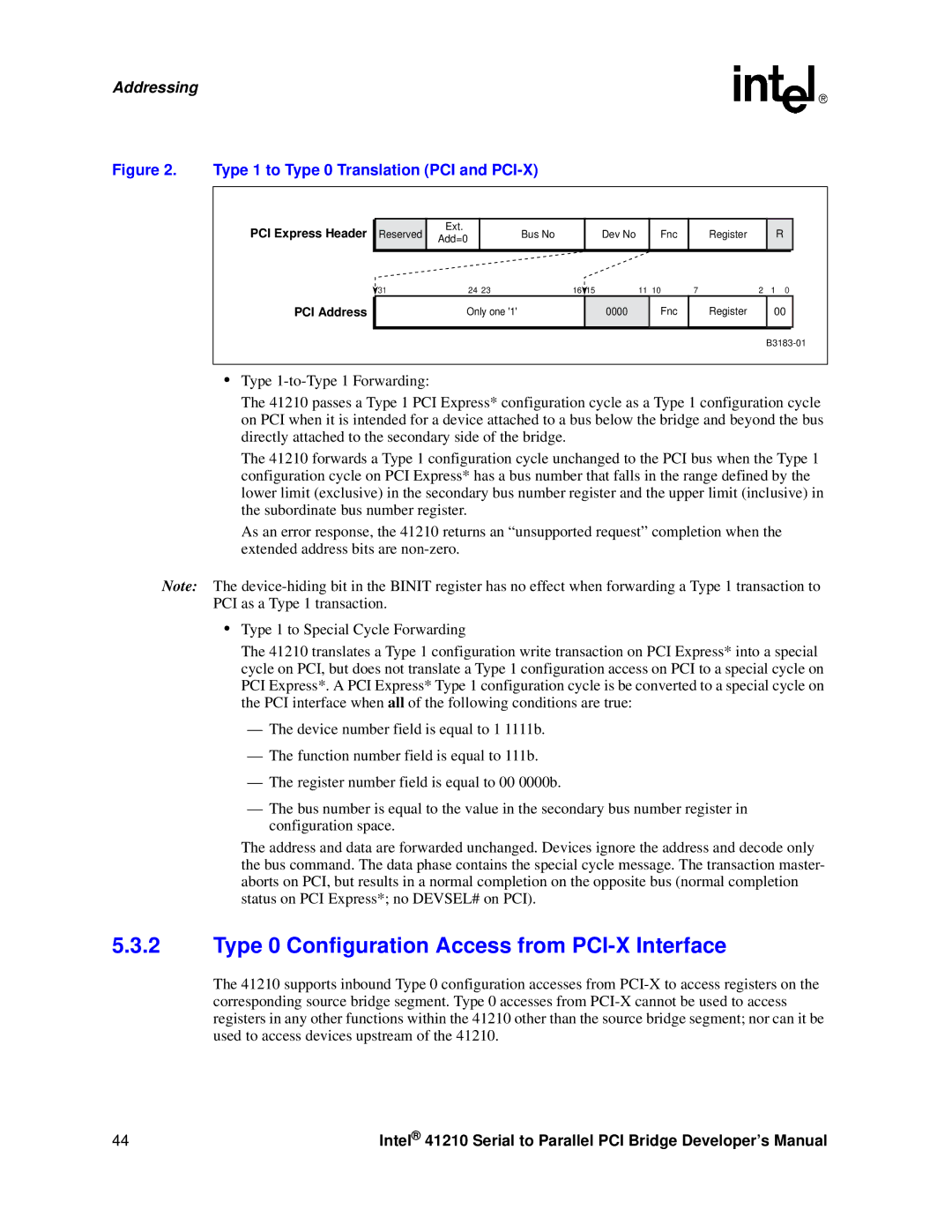

Figure 2. Type 1 to Type 0 Translation (PCI and PCI-X)

PCI Express Header

Reserved

Ext.

Add=0

Bus No

Dev No

Fnc

Register

R

31 30 29 28 27 26 | 25 24 23 22 21 20 | 19 | 18 17 16 15 14 13 | 12 11 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| |||

PCI Address |

| Only one '1' |

|

| 0000 | Fnc |

|

| Register |

| 00 |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

•Type

The 41210 passes a Type 1 PCI Express* configuration cycle as a Type 1 configuration cycle on PCI when it is intended for a device attached to a bus below the bridge and beyond the bus directly attached to the secondary side of the bridge.

The 41210 forwards a Type 1 configuration cycle unchanged to the PCI bus when the Type 1 configuration cycle on PCI Express* has a bus number that falls in the range defined by the lower limit (exclusive) in the secondary bus number register and the upper limit (inclusive) in the subordinate bus number register.

As an error response, the 41210 returns an “unsupported request” completion when the extended address bits are

Note: The

•Type 1 to Special Cycle Forwarding

The 41210 translates a Type 1 configuration write transaction on PCI Express* into a special cycle on PCI, but does not translate a Type 1 configuration access on PCI to a special cycle on PCI Express*. A PCI Express* Type 1 configuration cycle is be converted to a special cycle on the PCI interface when all of the following conditions are true:

—The device number field is equal to 1 1111b.

—The function number field is equal to 111b.

—The register number field is equal to 00 0000b.

—The bus number is equal to the value in the secondary bus number register in configuration space.

The address and data are forwarded unchanged. Devices ignore the address and decode only the bus command. The data phase contains the special cycle message. The transaction master- aborts on PCI, but results in a normal completion on the opposite bus (normal completion status on PCI Express*; no DEVSEL# on PCI).

5.3.2Type 0 Configuration Access from PCI-X Interface

The 41210 supports inbound Type 0 configuration accesses from

44 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |