Register Description

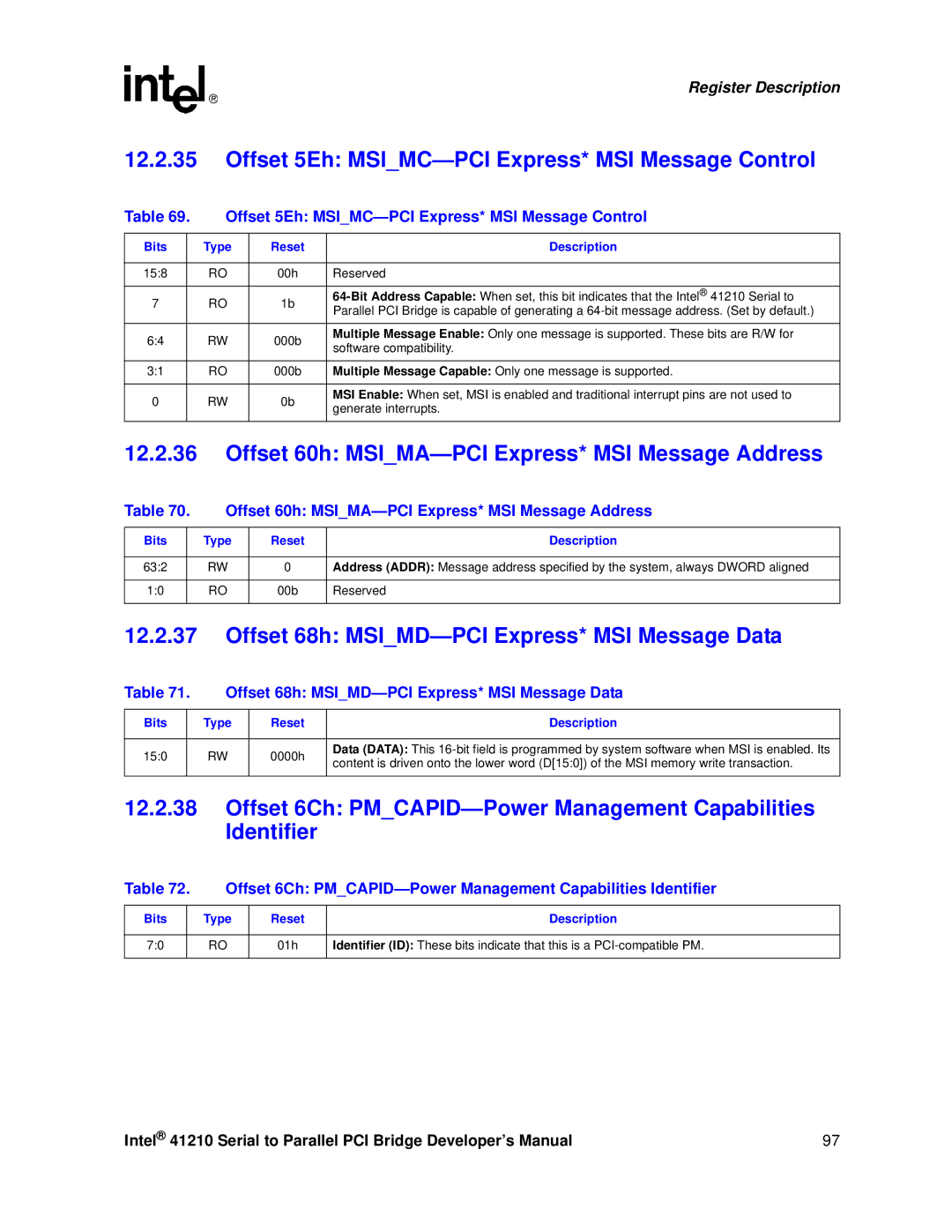

12.2.35Offset 5Eh: MSI_MC—PCI Express* MSI Message Control

Table 69. | Offset 5Eh: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

15:8 |

| RO | 00h | Reserved |

|

|

|

|

|

7 |

| RO | 1b | |

| Parallel PCI Bridge is capable of generating a | |||

|

|

|

| |

|

|

|

|

|

6:4 |

| RW | 000b | Multiple Message Enable: Only one message is supported. These bits are R/W for |

| software compatibility. | |||

|

|

|

| |

|

|

|

|

|

3:1 |

| RO | 000b | Multiple Message Capable: Only one message is supported. |

|

|

|

|

|

0 |

| RW | 0b | MSI Enable: When set, MSI is enabled and traditional interrupt pins are not used to |

| generate interrupts. | |||

|

|

|

| |

|

|

|

|

|

12.2.36Offset 60h: MSI_MA—PCI Express* MSI Message Address

Table 70. | Offset 60h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

63:2 |

| RW | 0 | Address (ADDR): Message address specified by the system, always DWORD aligned |

|

|

|

|

|

1:0 |

| RO | 00b | Reserved |

|

|

|

|

|

12.2.37Offset 68h: MSI_MD—PCI Express* MSI Message Data

Table 71. | Offset 68h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

15:0 |

| RW | 0000h | Data (DATA): This |

| content is driven onto the lower word (D[15:0]) of the MSI memory write transaction. | |||

|

|

|

| |

|

|

|

|

|

12.2.38Offset 6Ch: PM_CAPID—Power Management Capabilities Identifier

Table 72. | Offset 6Ch: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

7:0 |

| RO | 01h | Identifier (ID): These bits indicate that this is a |

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 97 |