Register Description

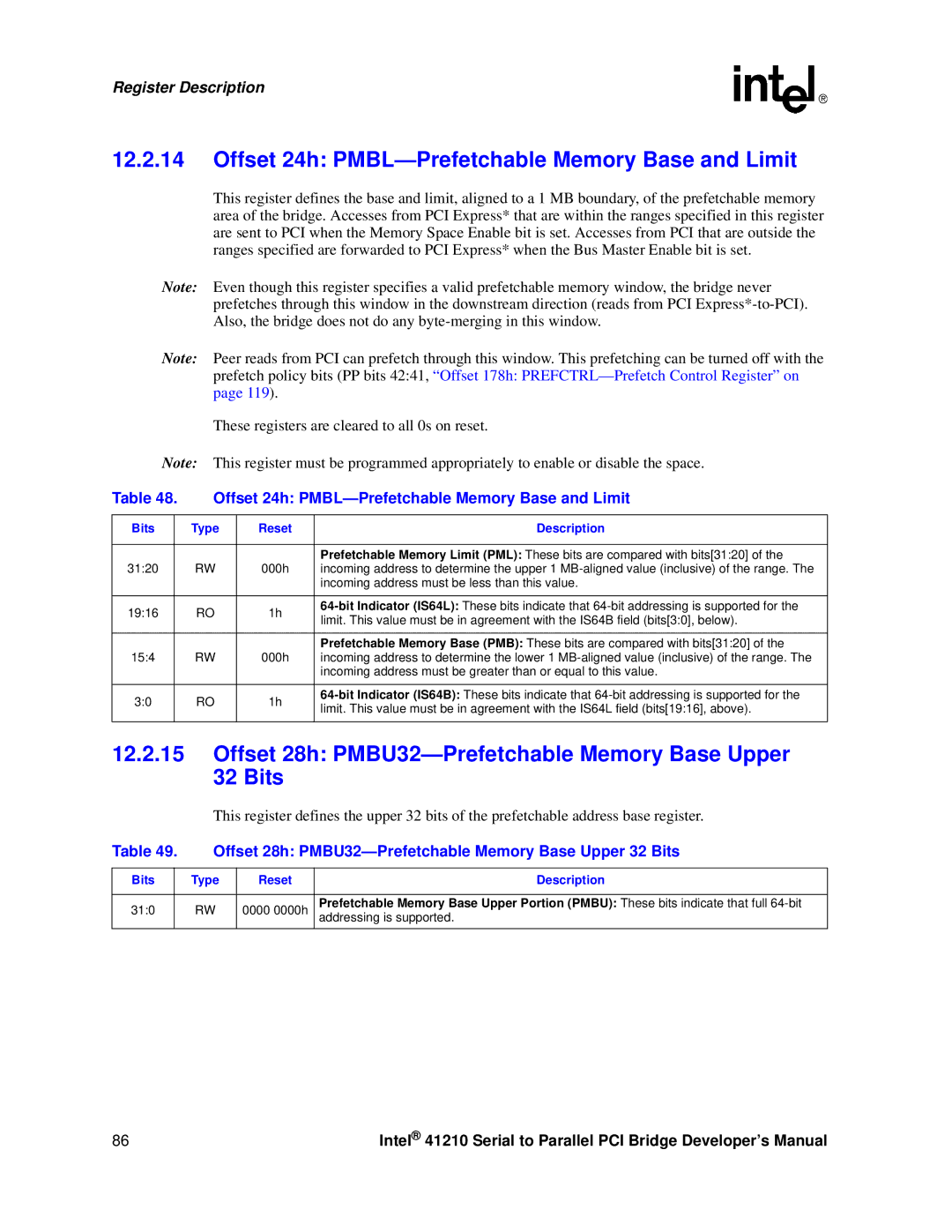

12.2.14Offset 24h: PMBL—Prefetchable Memory Base and Limit

This register defines the base and limit, aligned to a 1 MB boundary, of the prefetchable memory area of the bridge. Accesses from PCI Express* that are within the ranges specified in this register are sent to PCI when the Memory Space Enable bit is set. Accesses from PCI that are outside the ranges specified are forwarded to PCI Express* when the Bus Master Enable bit is set.

Note: Even though this register specifies a valid prefetchable memory window, the bridge never prefetches through this window in the downstream direction (reads from PCI

Note: Peer reads from PCI can prefetch through this window. This prefetching can be turned off with the prefetch policy bits (PP bits 42:41, “Offset 178h:

These registers are cleared to all 0s on reset.

Note: This register must be programmed appropriately to enable or disable the space.

Table 48. | Offset 24h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

31:20 |

| RW | 000h | Prefetchable Memory Limit (PML): These bits are compared with bits[31:20] of the |

| incoming address to determine the upper 1 | |||

|

|

|

| incoming address must be less than this value. |

|

|

|

|

|

19:16 |

| RO | 1h | |

| limit. This value must be in agreement with the IS64B field (bits[3:0], below). | |||

|

|

|

| |

|

|

|

|

|

|

|

|

| Prefetchable Memory Base (PMB): These bits are compared with bits[31:20] of the |

15:4 |

| RW | 000h | incoming address to determine the lower 1 |

|

|

|

| incoming address must be greater than or equal to this value. |

|

|

|

|

|

3:0 |

| RO | 1h | |

| limit. This value must be in agreement with the IS64L field (bits[19:16], above). | |||

|

|

|

| |

|

|

|

|

|

12.2.15Offset 28h: PMBU32—Prefetchable Memory Base Upper 32 Bits

This register defines the upper 32 bits of the prefetchable address base register.

Table 49. Offset 28h: PMBU32—Prefetchable Memory Base Upper 32 Bits

Bits | Type | Reset | Description |

|

|

|

|

31:0 | RW | 0000 0000h | Prefetchable Memory Base Upper Portion (PMBU): These bits indicate that full |

|

|

| addressing is supported. |

86 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |