| Transaction Ordering |

Transaction Ordering | 6 |

|

|

The Intel® 41210 Serial to Parallel PCI Bridge (called hereafter the 41210 Bridge or 41210) follows the

Accesses to the internal 41210 configuration registers follow no ordering relationship with respect to transactions moving to and from PCI and PCI Express* buses. This means that upstream memory and configuration reads and writes (when enabled via the BINIT register) are completed out of order with the transactions pending in the 41210 upstream queues towards PCI Express*. Downstream memory/configuration transactions to the internal register space can complete out of order with respect to transactions pending in the downstream queues towards PCI. Software must be aware that any semaphore mechanism implemented through the internal 41210 register space requires a dummy read to the PCI or PCI Express* space to push the writes that are pending in the 41210 queues in either direction. The ordering tables in the next two sections do not consider these transactions.

6.1Upstream Transaction Ordering

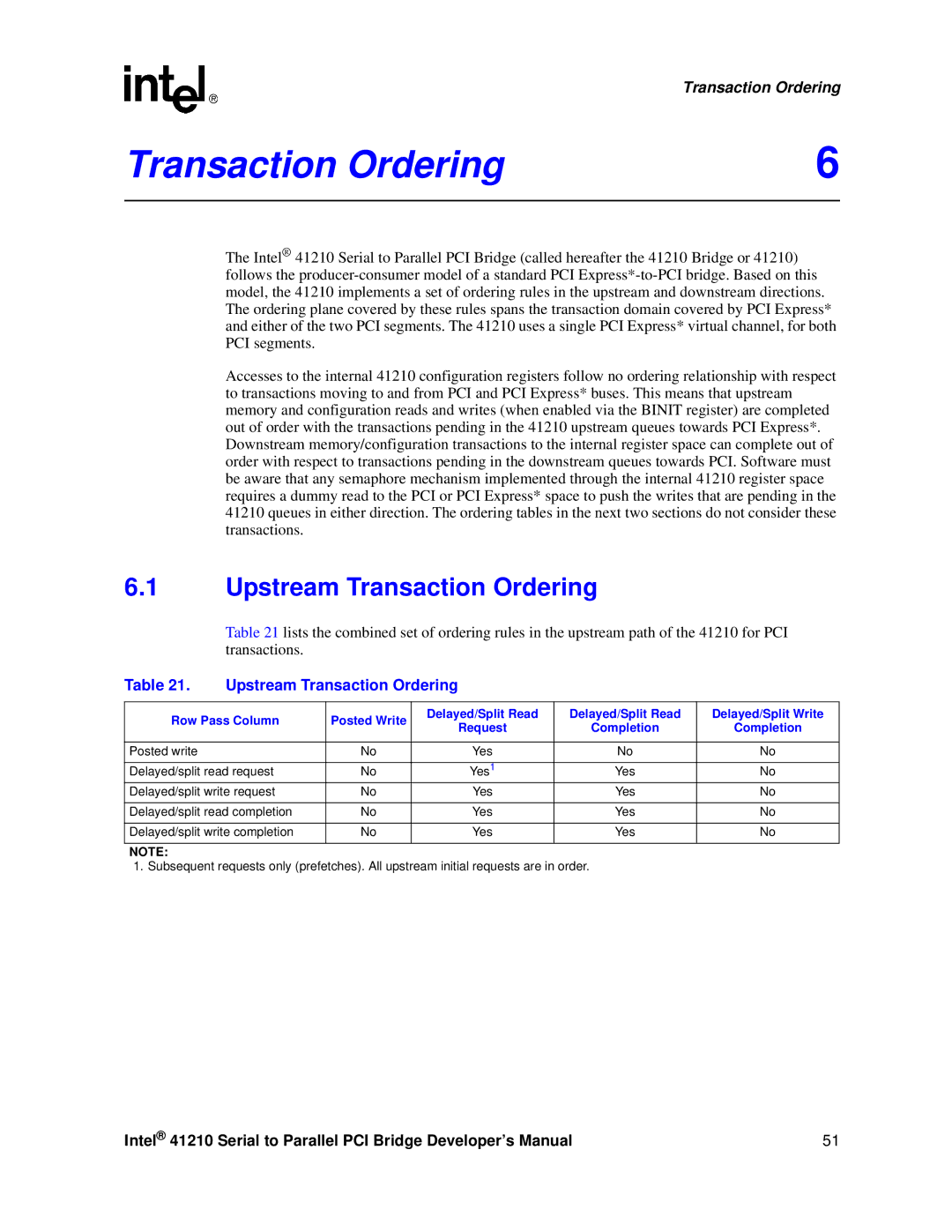

Table 21 lists the combined set of ordering rules in the upstream path of the 41210 for PCI transactions.

Table 21. | Upstream Transaction Ordering |

|

| |||

|

|

|

|

|

| |

Row Pass Column | Posted Write | Delayed/Split Read | Delayed/Split Read | Delayed/Split Write | ||

Request | Completion | Completion | ||||

|

|

| ||||

|

|

|

|

|

| |

Posted write |

| No | Yes | No | No | |

|

|

|

|

| ||

Delayed/split read request | No | Yes1 | Yes | No | ||

Delayed/split write request | No | Yes | Yes | No | ||

|

|

|

|

| ||

Delayed/split read completion | No | Yes | Yes | No | ||

|

|

|

|

| ||

Delayed/split write completion | No | Yes | Yes | No | ||

|

|

|

|

|

| |

NOTE: |

|

|

|

|

| |

1. Subsequent requests only (prefetches). All upstream initial requests are in order.

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 51 |