Register Description

12.2.67Offset 300h:

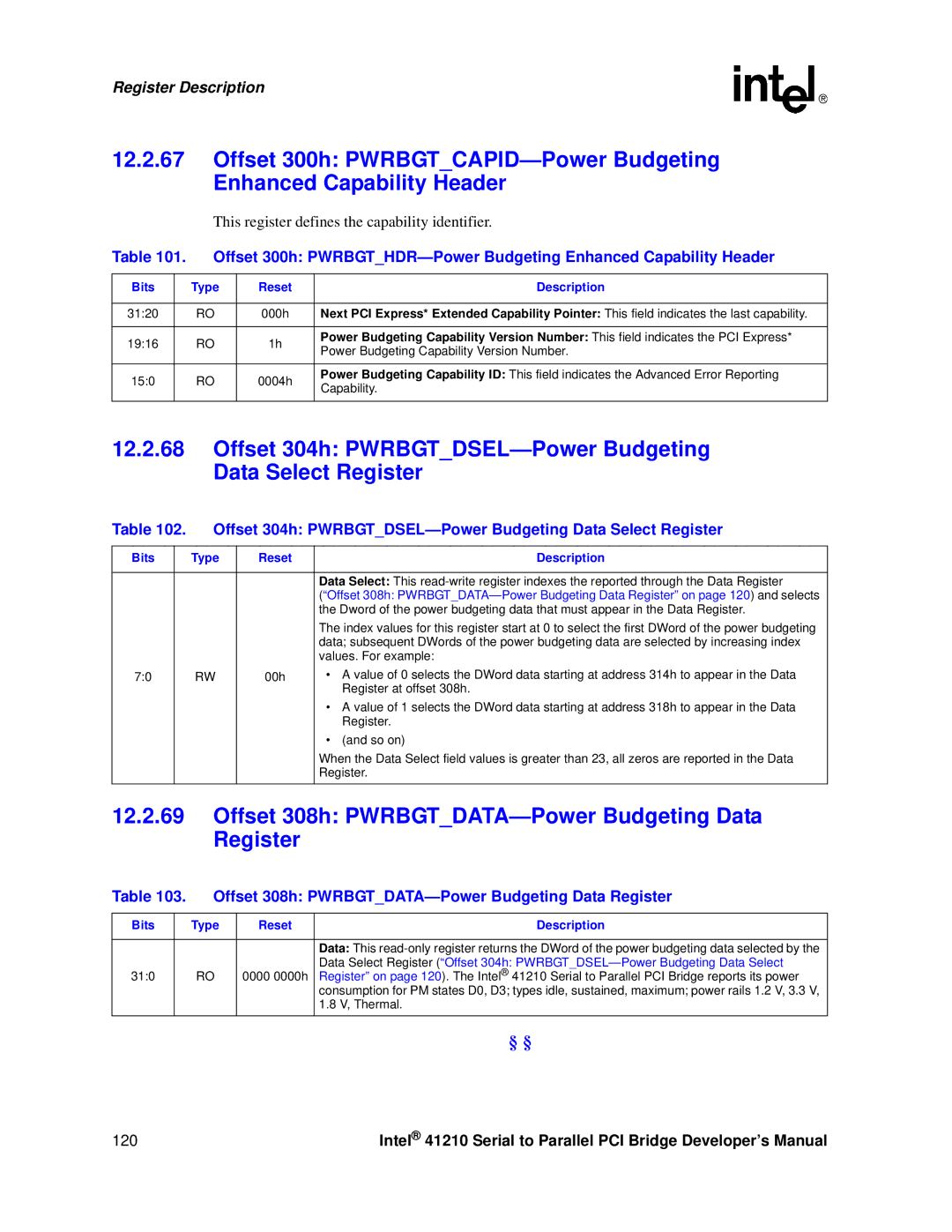

This register defines the capability identifier.

Table 101. | Offset 300h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

31:20 |

| RO | 000h | Next PCI Express* Extended Capability Pointer: This field indicates the last capability. |

|

|

|

|

|

19:16 |

| RO | 1h | Power Budgeting Capability Version Number: This field indicates the PCI Express* |

| Power Budgeting Capability Version Number. | |||

|

|

|

| |

|

|

|

|

|

15:0 |

| RO | 0004h | Power Budgeting Capability ID: This field indicates the Advanced Error Reporting |

| Capability. | |||

|

|

|

| |

|

|

|

|

|

12.2.68Offset 304h: PWRBGT_DSEL—Power Budgeting Data Select Register

Table 102. | Offset 304h: | ||||

|

|

|

|

|

|

Bits |

| Type | Reset |

| Description |

|

|

|

|

| |

|

|

|

| Data Select: This | |

|

|

|

| (“Offset 308h: | |

|

|

|

| the Dword of the power budgeting data that must appear in the Data Register. | |

|

|

|

| The index values for this register start at 0 to select the first DWord of the power budgeting | |

|

|

|

| data; subsequent DWords of the power budgeting data are selected by increasing index | |

|

|

|

| values. For example: | |

7:0 |

| RW | 00h | • | A value of 0 selects the DWord data starting at address 314h to appear in the Data |

|

|

|

|

| Register at offset 308h. |

|

|

|

| • A value of 1 selects the DWord data starting at address 318h to appear in the Data | |

|

|

|

|

| Register. |

|

|

|

| • | (and so on) |

|

|

|

| When the Data Select field values is greater than 23, all zeros are reported in the Data | |

|

|

|

| Register. | |

|

|

|

|

|

|

12.2.69Offset 308h: PWRBGT_DATA—Power Budgeting Data Register

Table 103. | Offset 308h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

|

|

|

| Data: This |

|

|

|

| Data Select Register (“Offset 304h: |

31:0 |

| RO | 0000 0000h | Register” on page 120). The Intel® 41210 Serial to Parallel PCI Bridge reports its power |

|

|

|

| consumption for PM states D0, D3; types idle, sustained, maximum; power rails 1.2 V, 3.3 V, |

|

|

|

| 1.8 V, Thermal. |

|

|

|

| § § |

120 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |