Register Description

12.2.11Offset 1Ch: IOBL—I/O Base and Limit

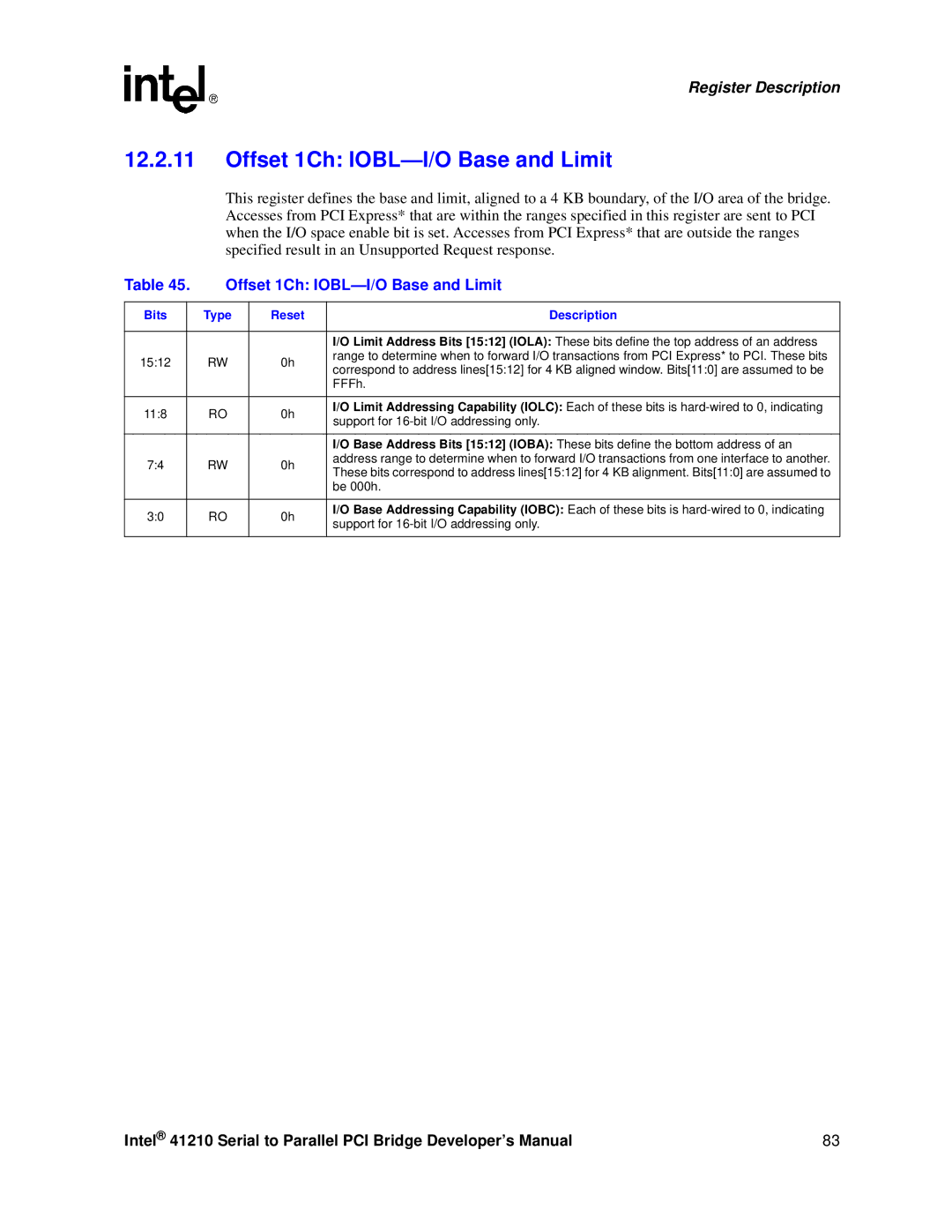

This register defines the base and limit, aligned to a 4 KB boundary, of the I/O area of the bridge. Accesses from PCI Express* that are within the ranges specified in this register are sent to PCI when the I/O space enable bit is set. Accesses from PCI Express* that are outside the ranges specified result in an Unsupported Request response.

Table 45. | Offset 1Ch: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

|

|

|

| I/O Limit Address Bits [15:12] (IOLA): These bits define the top address of an address |

15:12 |

| RW | 0h | range to determine when to forward I/O transactions from PCI Express* to PCI. These bits |

| correspond to address lines[15:12] for 4 KB aligned window. Bits[11:0] are assumed to be | |||

|

|

|

| |

|

|

|

| FFFh. |

|

|

|

|

|

11:8 |

| RO | 0h | I/O Limit Addressing Capability (IOLC): Each of these bits is |

| support for | |||

|

|

|

| |

|

|

|

|

|

|

|

|

| I/O Base Address Bits [15:12] (IOBA): These bits define the bottom address of an |

7:4 |

| RW | 0h | address range to determine when to forward I/O transactions from one interface to another. |

| These bits correspond to address lines[15:12] for 4 KB alignment. Bits[11:0] are assumed to | |||

|

|

|

| |

|

|

|

| be 000h. |

|

|

|

|

|

3:0 |

| RO | 0h | I/O Base Addressing Capability (IOBC): Each of these bits is |

| support for | |||

|

|

|

| |

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 83 |