Register Description

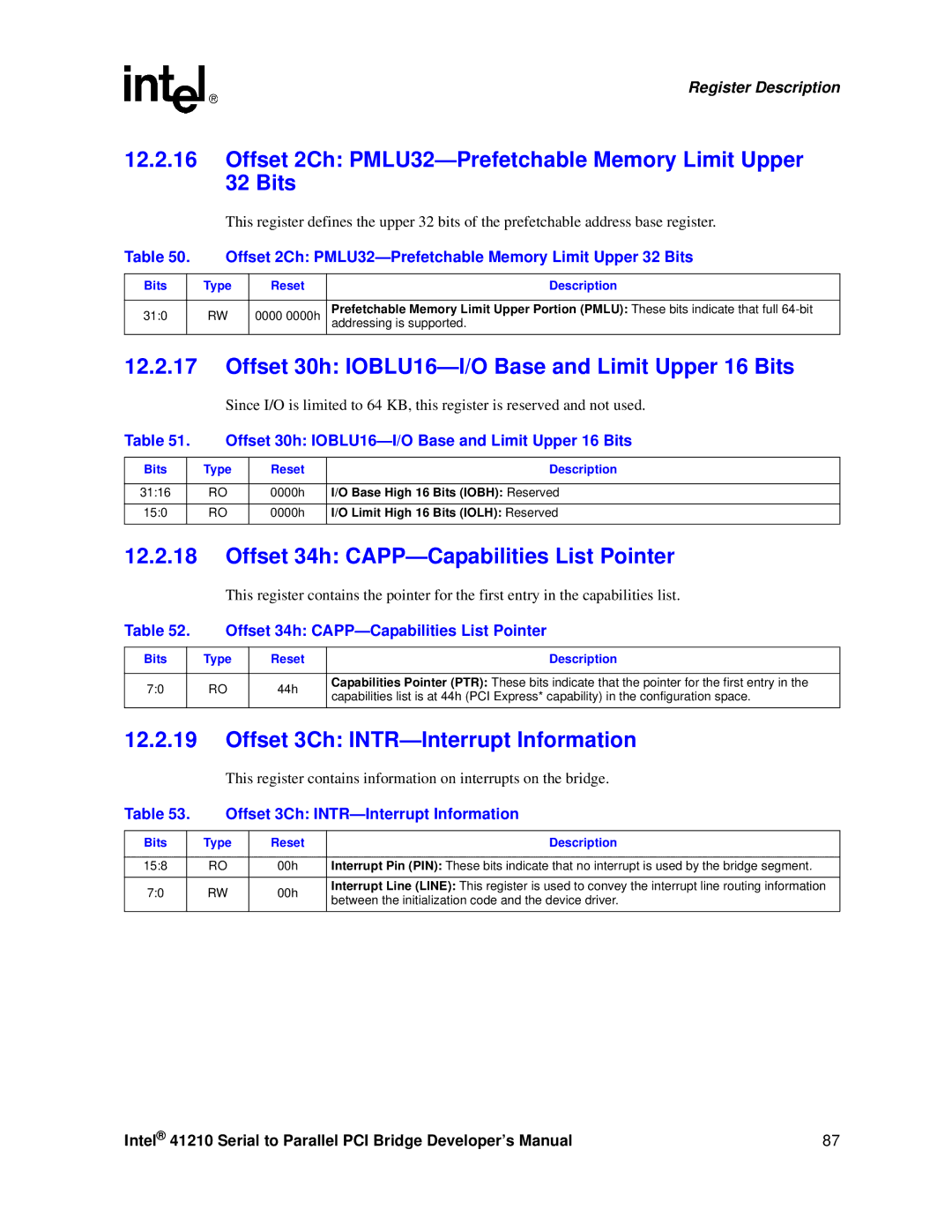

12.2.16Offset 2Ch: PMLU32—Prefetchable Memory Limit Upper 32 Bits

This register defines the upper 32 bits of the prefetchable address base register.

Table 50. Offset 2Ch: PMLU32—Prefetchable Memory Limit Upper 32 Bits

Bits | Type | Reset | Description |

|

|

|

|

31:0 | RW | 0000 0000h | Prefetchable Memory Limit Upper Portion (PMLU): These bits indicate that full |

|

|

| addressing is supported. |

12.2.17Offset 30h: IOBLU16—I/O Base and Limit Upper 16 Bits

Since I/O is limited to 64 KB, this register is reserved and not used.

Table 51. | Offset 30h: | ||||

|

|

|

|

|

|

Bits |

| Type | Reset |

| Description |

|

|

|

|

|

|

31:16 |

| RO | 0000h | I/O Base High 16 | Bits (IOBH): Reserved |

|

|

|

|

|

|

15:0 |

| RO | 0000h | I/O Limit High 16 | Bits (IOLH): Reserved |

|

|

|

|

|

|

12.2.18Offset 34h: CAPP—Capabilities List Pointer

This register contains the pointer for the first entry in the capabilities list.

Table 52. | Offset 34h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

7:0 |

| RO | 44h | Capabilities Pointer (PTR): These bits indicate that the pointer for the first entry in the |

| capabilities list is at 44h (PCI Express* capability) in the configuration space. | |||

|

|

|

| |

12.2.19Offset 3Ch: INTR—Interrupt Information

This register contains information on interrupts on the bridge.

Table 53. | Offset 3Ch: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

15:8 |

| RO | 00h | Interrupt Pin (PIN): These bits indicate that no interrupt is used by the bridge segment. |

|

|

|

|

|

7:0 |

| RW | 00h | Interrupt Line (LINE): This register is used to convey the interrupt line routing information |

| between the initialization code and the device driver. | |||

|

|

|

| |

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 87 |