Register Description

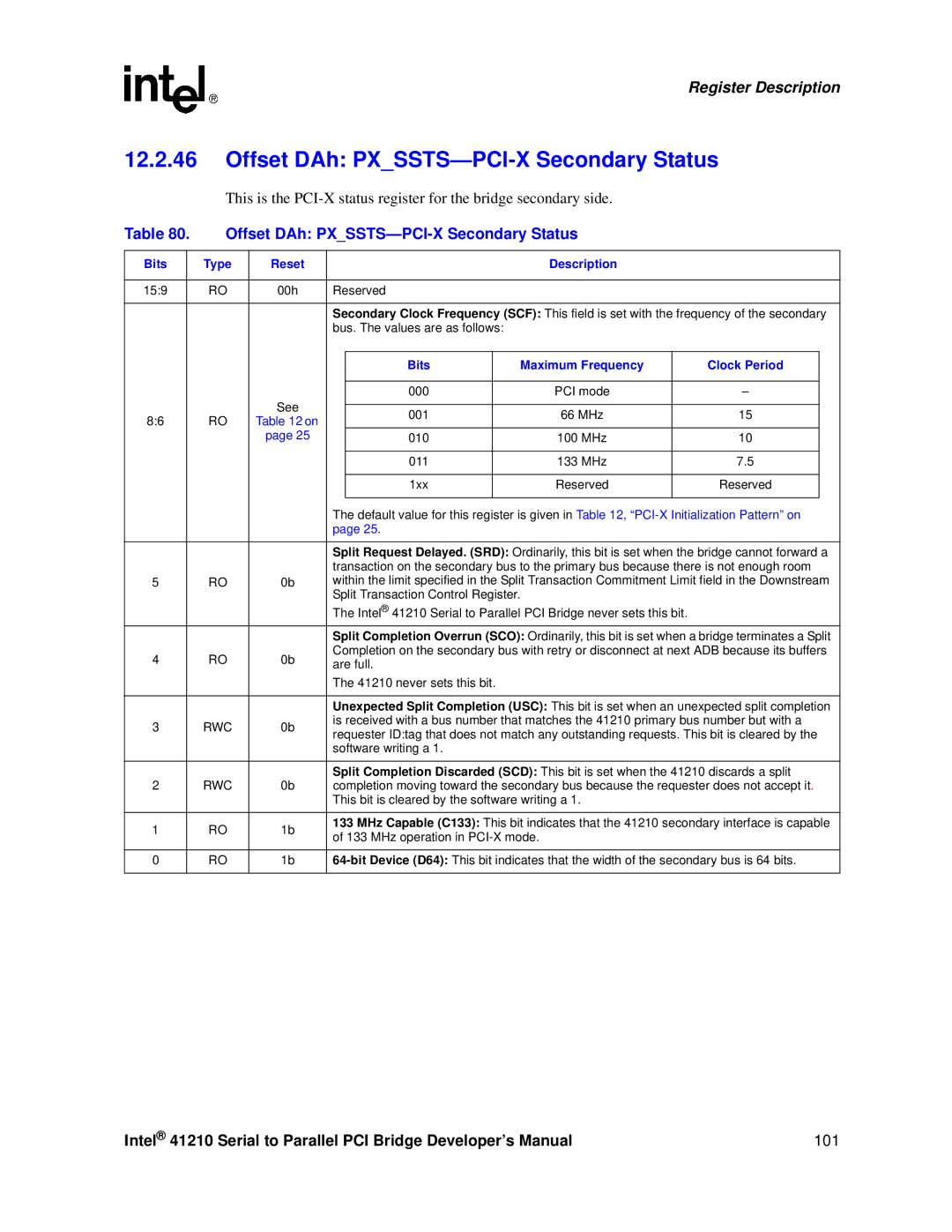

12.2.46Offset DAh: PX_SSTS—PCI-X Secondary Status

This is the

Table 80. | Offset DAh: |

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

Bits |

| Type | Reset |

|

|

| Description |

|

| |

|

|

|

|

|

|

|

|

|

|

|

15:9 |

| RO | 00h | Reserved |

|

|

|

| ||

|

|

|

|

|

|

|

|

| ||

|

|

|

| Secondary Clock Frequency (SCF): This field is set with the frequency of the secondary | ||||||

|

|

|

| bus. The values are as follows: |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Bits |

| Maximum Frequency |

| Clock Period |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| See |

| 000 |

| PCI mode |

| – |

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

| 001 |

| 66 MHz |

| 15 |

| |

8:6 |

| RO | Table 12 on |

|

|

|

| |||

|

|

|

|

|

|

|

| |||

|

|

| page 25 |

| 010 |

| 100 MHz |

| 10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 011 |

| 133 MHz |

| 7.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1xx |

| Reserved |

| Reserved |

|

|

|

|

|

|

|

|

|

| ||

|

|

|

| The default value for this register is given in Table 12, | ||||||

|

|

|

| page 25. |

|

|

|

| ||

|

|

|

|

|

|

|

|

| ||

|

|

|

| Split Request Delayed. (SRD): Ordinarily, this bit is set when the bridge cannot forward a | ||||||

|

|

|

| transaction on the secondary bus to the primary bus because there is not enough room | ||||||

5 |

| RO | 0b | within the limit specified in the Split Transaction Commitment Limit field in the Downstream | ||||||

|

|

|

| Split Transaction Control Register. |

|

| ||||

|

|

|

| The Intel® 41210 Serial to Parallel PCI Bridge never sets this bit. |

|

| ||||

|

|

|

| Split Completion Overrun (SCO): Ordinarily, this bit is set when a bridge terminates a Split | ||||||

4 |

| RO | 0b | Completion on the secondary bus with retry or disconnect at next ADB because its buffers | ||||||

| are full. |

|

|

|

| |||||

|

|

|

|

|

|

|

| |||

|

|

|

| The 41210 never sets this bit. |

|

|

|

| ||

|

|

|

|

|

|

|

|

| ||

|

|

|

| Unexpected Split Completion (USC): This bit is set when an unexpected split completion | ||||||

3 |

| RWC | 0b | is received with a bus number that matches the 41210 primary bus number but with a | ||||||

| requester ID:tag that does not match any outstanding requests. This bit is cleared by the | |||||||||

|

|

|

| |||||||

|

|

|

| software writing a 1. |

|

|

|

| ||

|

|

|

|

|

|

|

|

| ||

|

|

|

| Split Completion Discarded (SCD): This bit is set when the 41210 discards a split | ||||||

2 |

| RWC | 0b | completion moving toward the secondary bus because the requester does not accept it. | ||||||

|

|

|

| This bit is cleared by the software writing a 1. |

|

| ||||

|

|

|

|

|

|

|

|

| ||

1 |

| RO | 1b | 133 MHz Capable (C133): This bit indicates that the 41210 secondary interface is capable | ||||||

| of 133 MHz operation in |

|

| |||||||

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| ||

0 |

| RO | 1b | |||||||

|

|

|

|

|

|

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 101 |