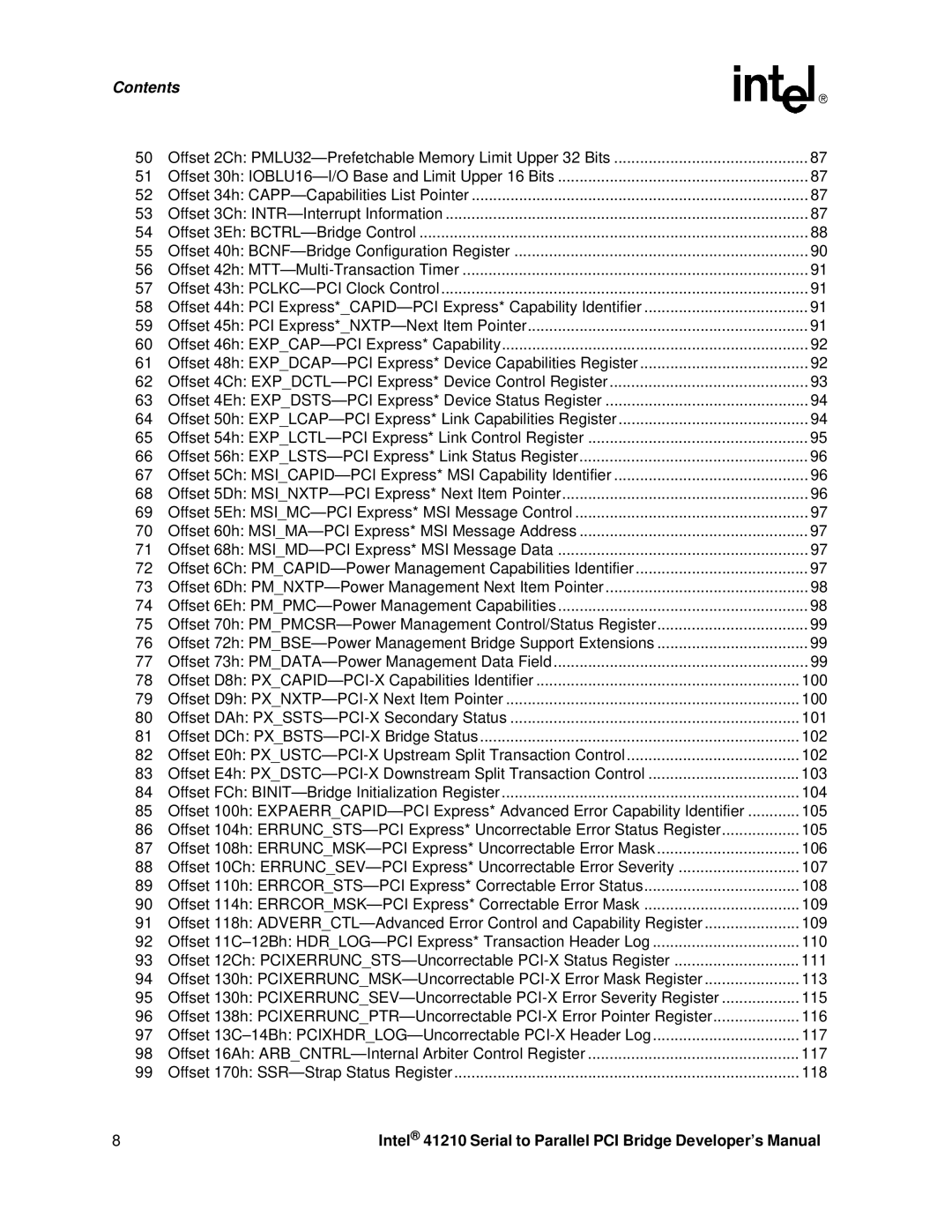

Contents |

| |

50 | Offset 2Ch: | 87 |

51 | Offset 30h: | 87 |

52 | Offset 34h: | 87 |

53 | Offset 3Ch: | 87 |

54 | Offset 3Eh: | 88 |

55 | Offset 40h: | 90 |

56 | Offset 42h: | 91 |

57 | Offset 43h: | 91 |

58 | Offset 44h: PCI | 91 |

59 | Offset 45h: PCI | 91 |

60 | Offset 46h: | 92 |

61 | Offset 48h: | 92 |

62 | Offset 4Ch: | 93 |

63 | Offset 4Eh: | 94 |

64 | Offset 50h: | 94 |

65 | Offset 54h: | 95 |

66 | Offset 56h: | 96 |

67 | Offset 5Ch: | 96 |

68 | Offset 5Dh: | 96 |

69 | Offset 5Eh: | 97 |

70 | Offset 60h: | 97 |

71 | Offset 68h: | 97 |

72 | Offset 6Ch: | 97 |

73 | Offset 6Dh: | 98 |

74 | Offset 6Eh: | 98 |

75 | Offset 70h: | 99 |

76 | Offset 72h: | 99 |

77 | Offset 73h: | 99 |

78 | Offset D8h: | 100 |

79 | Offset D9h: | 100 |

80 | Offset DAh: | 101 |

81 | Offset DCh: | 102 |

82 | Offset E0h: | 102 |

83 | Offset E4h: | 103 |

84 | Offset FCh: | 104 |

85 | Offset 100h: | 105 |

86 | Offset 104h: | 105 |

87 | Offset 108h: | 106 |

88 | Offset 10Ch: | 107 |

89 | Offset 110h: | 108 |

90 | Offset 114h: | 109 |

91 | Offset 118h: | 109 |

92 | Offset | 110 |

93 | Offset 12Ch: | 111 |

94 | Offset 130h: | 113 |

95 | Offset 130h: | 115 |

96 | Offset 138h: | 116 |

97 | Offset | 117 |

98 | Offset 16Ah: | 117 |

99 | Offset 170h: | 118 |

8 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |