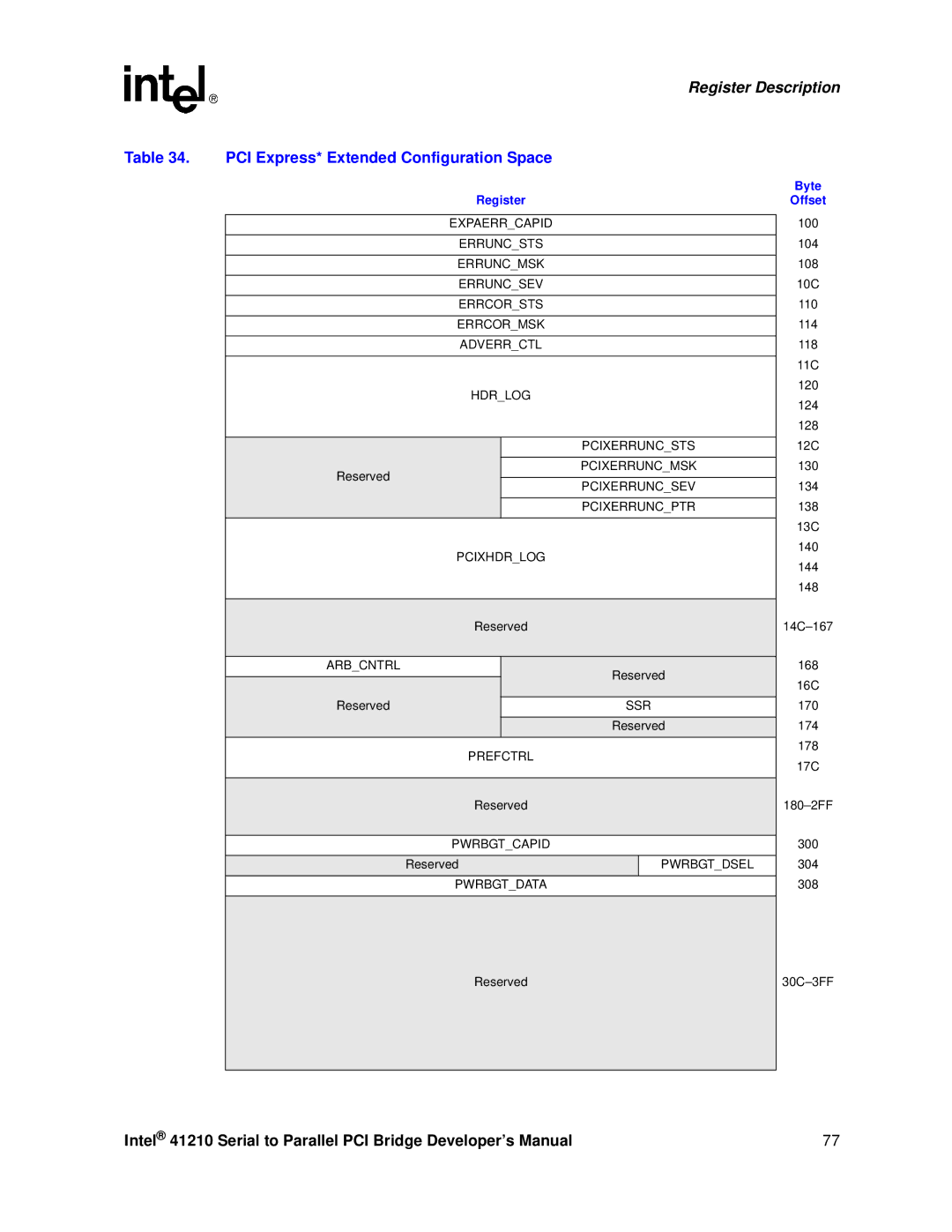

Register Description

Table 34. PCI Express* Extended Configuration Space

Register

EXPAERR_CAPID

ERRUNC_STS

ERRUNC_MSK

ERRUNC_SEV

ERRCOR_STS

ERRCOR_MSK

ADVERR_CTL

HDR_LOG

|

| PCIXERRUNC_STS |

|

|

|

Reserved |

| PCIXERRUNC_MSK |

|

| |

| PCIXERRUNC_SEV | |

|

| |

|

|

|

|

| PCIXERRUNC_PTR |

| PCIXHDR_LOG | |

|

|

|

| Reserved | |

|

|

|

ARB_CNTRL |

| Reserved |

|

| |

Reserved |

| |

|

| |

| SSR | |

|

|

|

|

| Reserved |

| PREFCTRL | |

Reserved

PWRBGT_CAPID

ReservedPWRBGT_DSEL

PWRBGT_DATA

Reserved

Byte

Offset

100

104

108

10C

110

114

118

11C

120

124

128

12C

130

134

138

13C

140

144

148

168

16C

170

174

178

17C

300

304

308

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 77 |