Register Description |

|

| |||

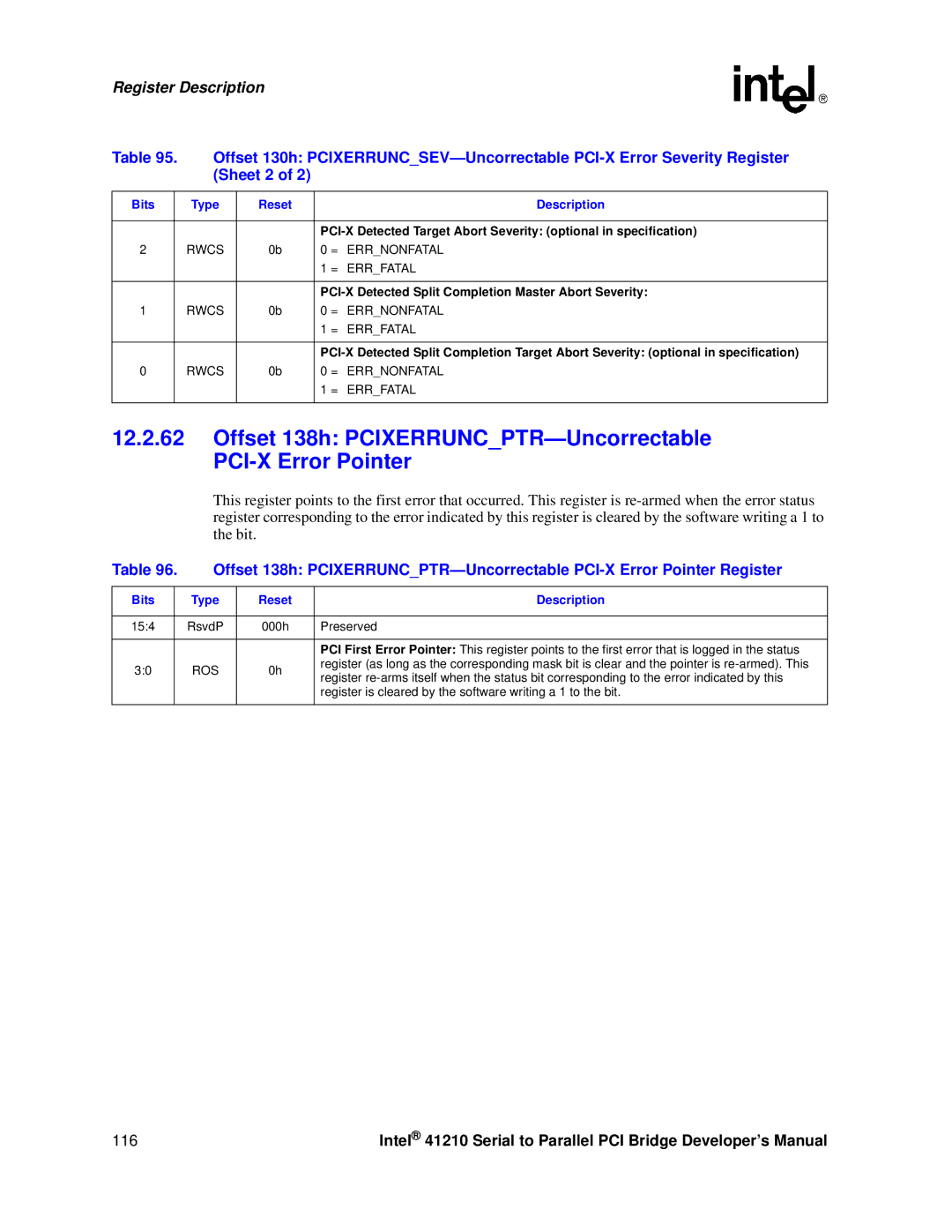

Table 95. | Offset 130h: | ||||

|

| (Sheet 2 of 2) |

|

| |

|

|

|

|

|

|

Bits |

| Type | Reset |

| Description |

|

|

|

|

| |

|

|

|

| ||

2 |

| RWCS | 0b | 0 | = ERR_NONFATAL |

|

|

|

| 1 | = ERR_FATAL |

|

|

|

|

| |

|

|

|

|

| |

1 |

| RWCS | 0b | 0 | = ERR_NONFATAL |

|

|

|

| 1 | = ERR_FATAL |

|

|

|

|

| |

|

|

|

| ||

0 |

| RWCS | 0b | 0 | = ERR_NONFATAL |

|

|

|

| 1 | = ERR_FATAL |

|

|

|

|

|

|

12.2.62Offset 138h: PCIXERRUNC_PTR—Uncorrectable PCI-X Error Pointer

This register points to the first error that occurred. This register is

Table 96. | Offset 138h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

15:4 |

| RsvdP | 000h | Preserved |

|

|

|

|

|

|

|

|

| PCI First Error Pointer: This register points to the first error that is logged in the status |

3:0 |

| ROS | 0h | register (as long as the corresponding mask bit is clear and the pointer is |

| register | |||

|

|

|

| |

|

|

|

| register is cleared by the software writing a 1 to the bit. |

|

|

|

|

|

116 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |