Register Description |

|

| |||

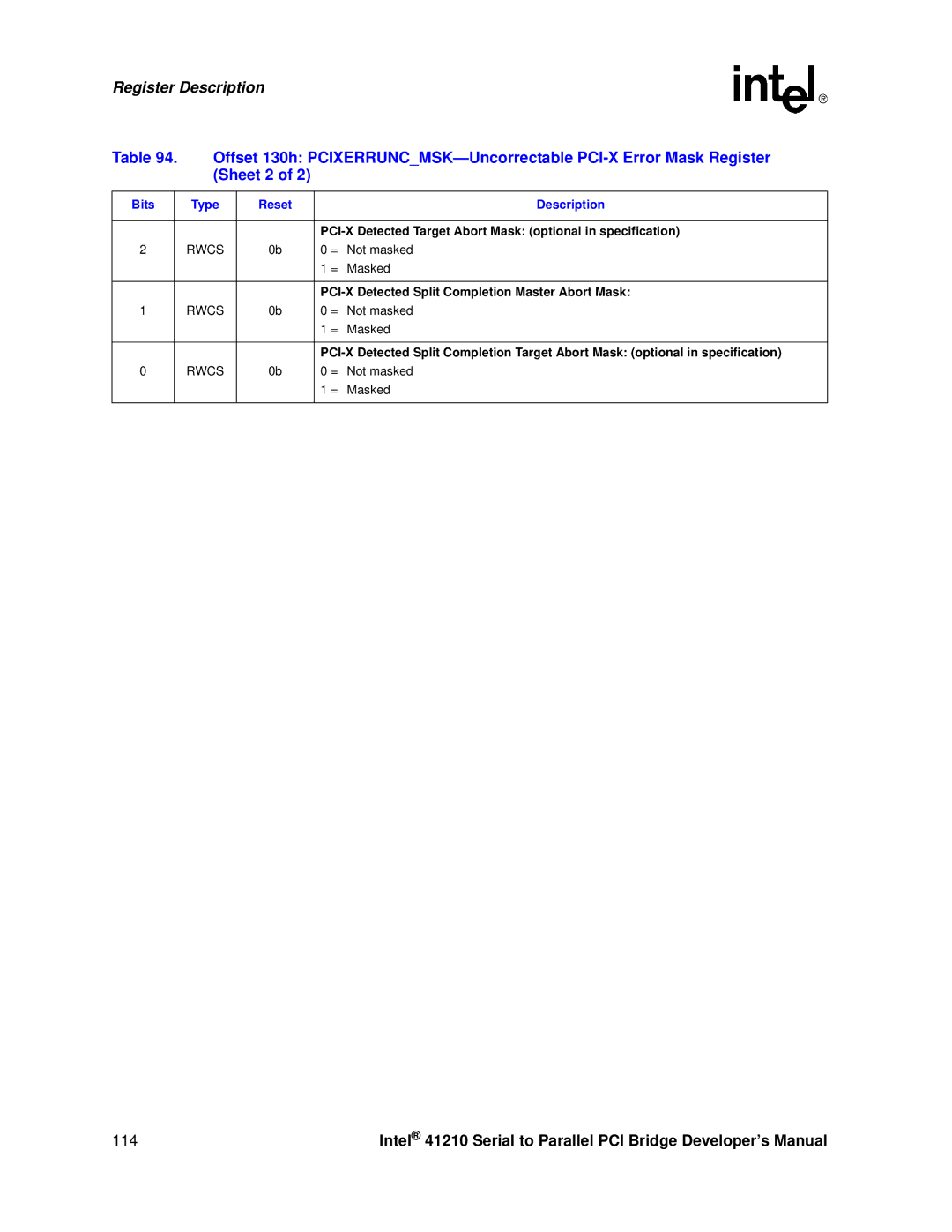

Table 94. | Offset 130h: | ||||

|

| (Sheet 2 of 2) |

|

| |

|

|

|

|

|

|

Bits |

| Type | Reset |

| Description |

|

|

|

|

| |

|

|

|

|

| |

2 |

| RWCS | 0b | 0 = | Not masked |

|

|

|

| 1 = | Masked |

|

|

|

|

| |

|

|

|

|

| |

1 |

| RWCS | 0b | 0 = | Not masked |

|

|

|

| 1 = | Masked |

|

|

|

|

| |

|

|

|

| ||

0 |

| RWCS | 0b | 0 = | Not masked |

|

|

|

| 1 = | Masked |

|

|

|

|

|

|

114 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |