System Management Bus Interface

8.2.2Configuration Writes

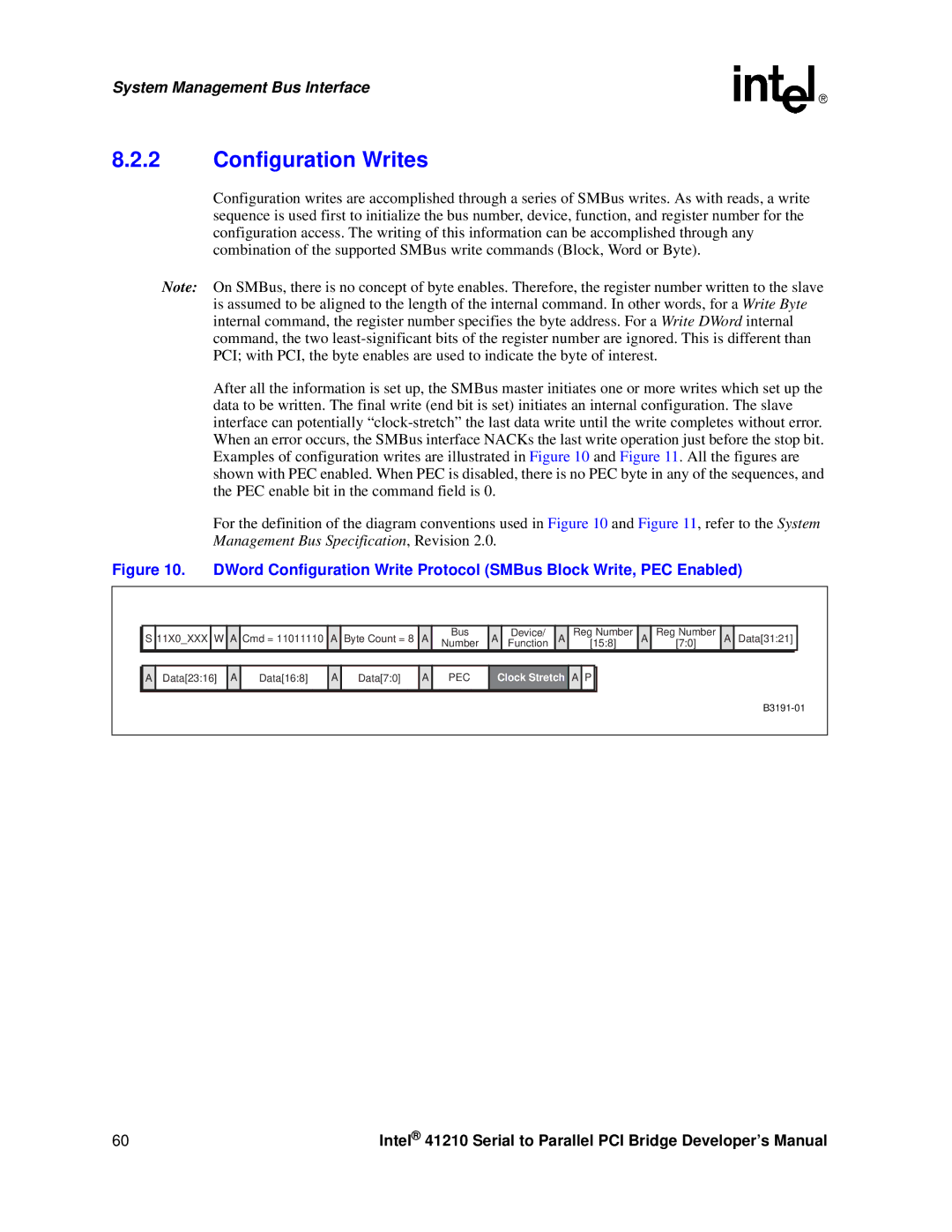

Configuration writes are accomplished through a series of SMBus writes. As with reads, a write sequence is used first to initialize the bus number, device, function, and register number for the configuration access. The writing of this information can be accomplished through any combination of the supported SMBus write commands (Block, Word or Byte).

Note: On SMBus, there is no concept of byte enables. Therefore, the register number written to the slave is assumed to be aligned to the length of the internal command. In other words, for a Write Byte internal command, the register number specifies the byte address. For a Write DWord internal command, the two

After all the information is set up, the SMBus master initiates one or more writes which set up the data to be written. The final write (end bit is set) initiates an internal configuration. The slave interface can potentially

For the definition of the diagram conventions used in Figure 10 and Figure 11, refer to the System Management Bus Specification, Revision 2.0.

Figure 10. DWord Configuration Write Protocol (SMBus Block Write, PEC Enabled)

S 11X0_XXX

W | A | Cmd = 11011110 | A | Byte Count = 8 | A | Bus | |

Number | |||||||

|

|

|

|

|

| ||

|

|

|

|

|

|

|

A

Device/

Function

A

Reg Number

[15:8]

A

Reg Number

[7:0]

A Data[31:21]

A Data[23:16] A

Data[16:8]

A

Data[7:0]

A

PEC

Clock Stretch

A P

60 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |