Register Description

12.2.61Offset 134h:

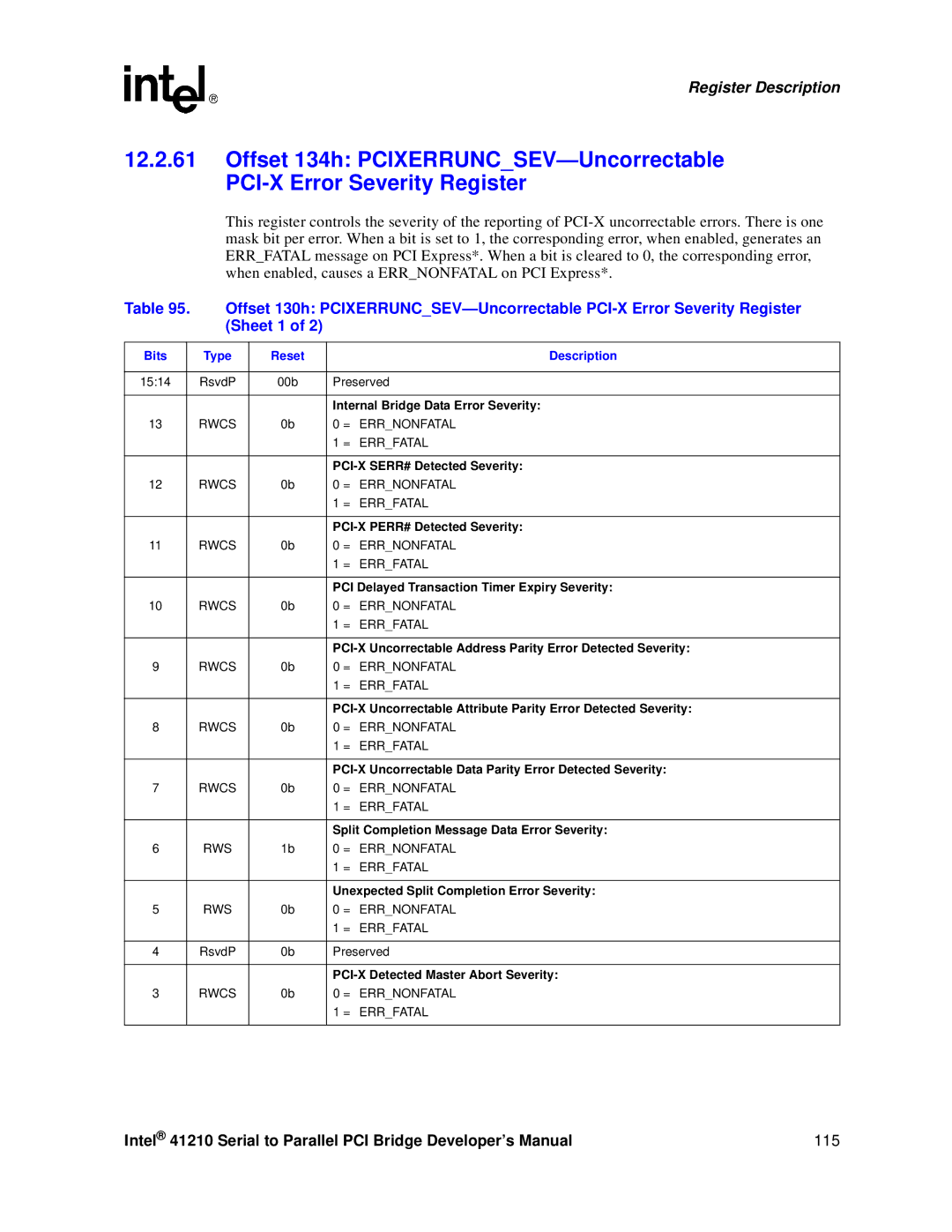

This register controls the severity of the reporting of

Table 95. Offset 130h:

Bits | Type | Reset |

| Description |

|

|

|

| |

15:14 | RsvdP | 00b | Preserved | |

|

|

|

| |

|

|

| Internal Bridge Data Error Severity: | |

13 | RWCS | 0b | 0 = | ERR_NONFATAL |

|

|

| 1 = | ERR_FATAL |

|

|

|

| |

|

|

|

| |

12 | RWCS | 0b | 0 = | ERR_NONFATAL |

|

|

| 1 = | ERR_FATAL |

|

|

|

| |

|

|

|

| |

11 | RWCS | 0b | 0 = | ERR_NONFATAL |

|

|

| 1 = | ERR_FATAL |

|

|

|

| |

|

|

| PCI Delayed Transaction Timer Expiry Severity: | |

10 | RWCS | 0b | 0 = | ERR_NONFATAL |

|

|

| 1 = | ERR_FATAL |

|

|

|

| |

|

|

|

| |

9 | RWCS | 0b | 0 = ERR_NONFATAL | |

|

|

| 1 = | ERR_FATAL |

|

|

|

| |

|

|

| ||

8 | RWCS | 0b | 0 = ERR_NONFATAL | |

|

|

| 1 = | ERR_FATAL |

|

|

|

| |

|

|

|

| |

7 | RWCS | 0b | 0 = ERR_NONFATAL | |

|

|

| 1 = | ERR_FATAL |

|

|

|

| |

|

|

| Split Completion Message Data Error Severity: | |

6 | RWS | 1b | 0 = | ERR_NONFATAL |

|

|

| 1 = | ERR_FATAL |

|

|

|

| |

|

|

| Unexpected Split Completion Error Severity: | |

5 | RWS | 0b | 0 = | ERR_NONFATAL |

|

|

| 1 = | ERR_FATAL |

|

|

|

| |

4 | RsvdP | 0b | Preserved | |

|

|

|

| |

|

|

|

| |

3 | RWCS | 0b | 0 = ERR_NONFATAL | |

|

|

| 1 = | ERR_FATAL |

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 115 |