System Management Bus Interface

8.2Initialization Sequence

All configuration read and writes are accomplished through SMBus write(s) followed by an SMBus read (for a read command). For configuration access, the SMBus write sequence is used to initialize the following parameters:

•Bus number

•Device/function number

•

Each of the parameters above is sent on the SMBus in separate bytes. The register number parameter is initialized with two bytes, and the 41210 ignores the most significant four bits of the second byte that initializes the register number.

The initialization of the information can be accomplished through any combination of the supported SMBus write commands (Block, Word or Byte). The internal command field for each write must specify the same internal command every time (read or write). After all the information is set up, the last write (end bit is set) initiates an internal read or write command. On an internal read, when the data is not available before the slave interface acknowledges this last write command (ACK), the slave “clock stretches” until the data returns to the SMBus interface unit. On an internal write, when the write is not complete before the slave interface acknowledges this last write command (ACK), the slave “clock stretches” until the write completes internally. When an error occurs (internal

8.2.1Configuration

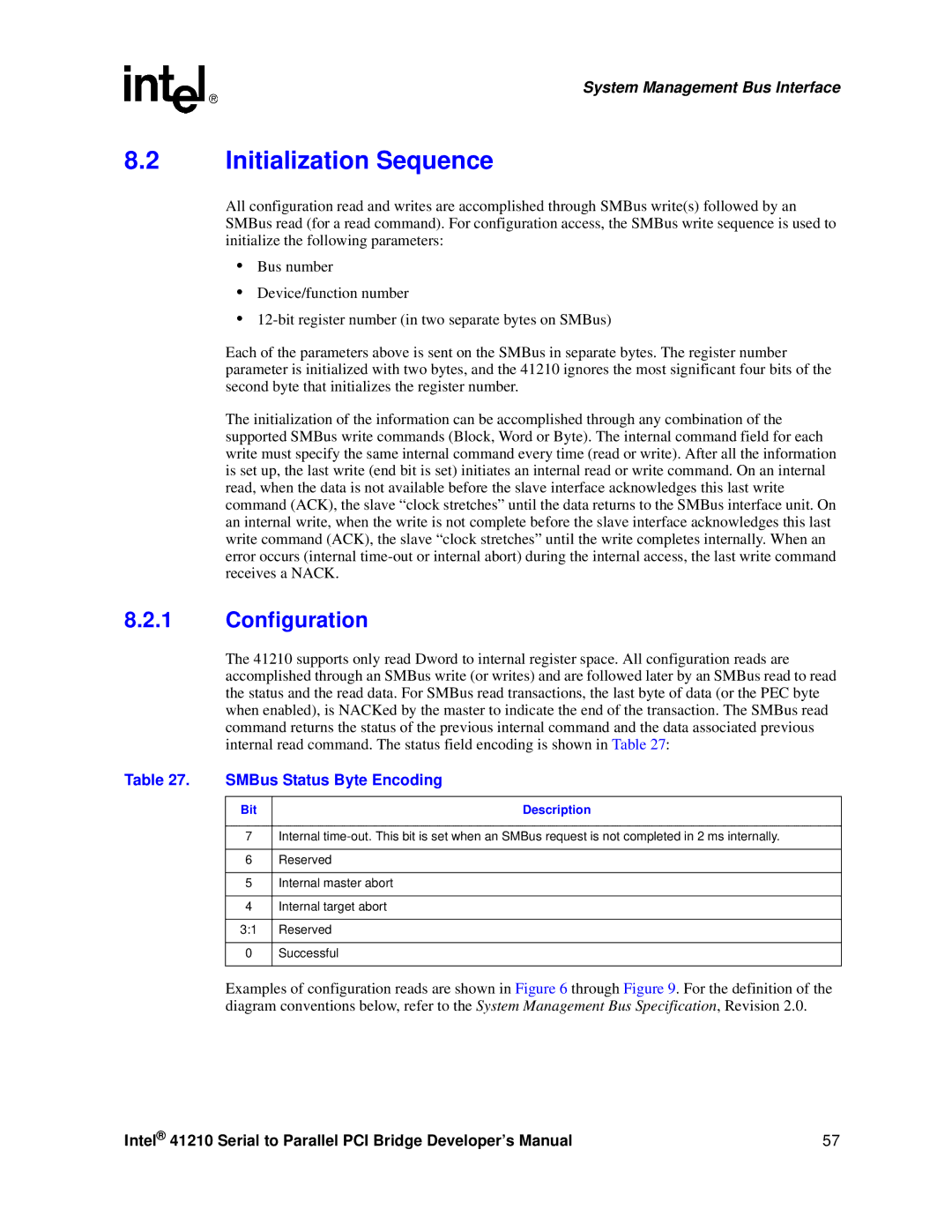

The 41210 supports only read Dword to internal register space. All configuration reads are accomplished through an SMBus write (or writes) and are followed later by an SMBus read to read the status and the read data. For SMBus read transactions, the last byte of data (or the PEC byte when enabled), is NACKed by the master to indicate the end of the transaction. The SMBus read command returns the status of the previous internal command and the data associated previous internal read command. The status field encoding is shown in Table 27:

Table 27. | SMBus Status Byte Encoding | |

|

|

|

| Bit | Description |

|

|

|

| 7 | Internal |

|

|

|

| 6 | Reserved |

|

|

|

| 5 | Internal master abort |

|

|

|

| 4 | Internal target abort |

|

|

|

| 3:1 | Reserved |

|

|

|

| 0 | Successful |

|

|

|

Examples of configuration reads are shown in Figure 6 through Figure 9. For the definition of the diagram conventions below, refer to the System Management Bus Specification, Revision 2.0.

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 57 |