Register Description |

| |||

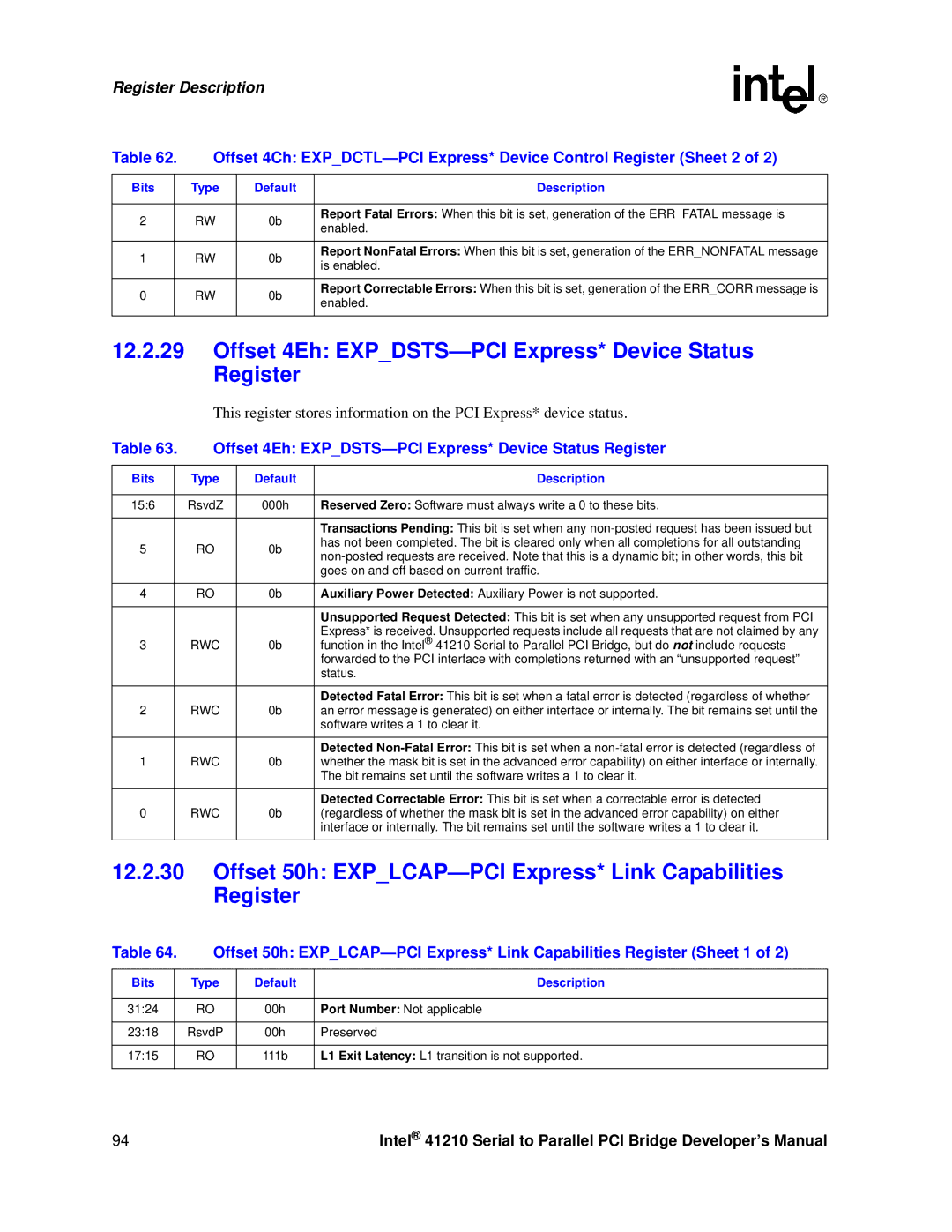

Table 62. | Offset 4Ch: | |||

|

|

|

|

|

Bits |

| Type | Default | Description |

|

|

|

|

|

2 |

| RW | 0b | Report Fatal Errors: When this bit is set, generation of the ERR_FATAL message is |

| enabled. | |||

|

|

|

| |

|

|

|

|

|

1 |

| RW | 0b | Report NonFatal Errors: When this bit is set, generation of the ERR_NONFATAL message |

| is enabled. | |||

|

|

|

| |

|

|

|

|

|

0 |

| RW | 0b | Report Correctable Errors: When this bit is set, generation of the ERR_CORR message is |

| enabled. | |||

|

|

|

| |

|

|

|

|

|

12.2.29Offset 4Eh: EXP_DSTS—PCI Express* Device Status Register

This register stores information on the PCI Express* device status.

Table 63. | Offset 4Eh: | |||

|

|

|

|

|

Bits |

| Type | Default | Description |

|

|

|

|

|

15:6 |

| RsvdZ | 000h | Reserved Zero: Software must always write a 0 to these bits. |

|

|

|

|

|

|

|

|

| Transactions Pending: This bit is set when any |

5 |

| RO | 0b | has not been completed. The bit is cleared only when all completions for all outstanding |

| ||||

|

|

|

| |

|

|

|

| goes on and off based on current traffic. |

|

|

|

|

|

4 |

| RO | 0b | Auxiliary Power Detected: Auxiliary Power is not supported. |

|

|

|

|

|

|

|

|

| Unsupported Request Detected: This bit is set when any unsupported request from PCI |

|

|

|

| Express* is received. Unsupported requests include all requests that are not claimed by any |

3 |

| RWC | 0b | function in the Intel® 41210 Serial to Parallel PCI Bridge, but do not include requests |

|

|

|

| forwarded to the PCI interface with completions returned with an “unsupported request” |

|

|

|

| status. |

|

|

|

|

|

|

|

|

| Detected Fatal Error: This bit is set when a fatal error is detected (regardless of whether |

2 |

| RWC | 0b | an error message is generated) on either interface or internally. The bit remains set until the |

|

|

|

| software writes a 1 to clear it. |

|

|

|

|

|

|

|

|

| Detected |

1 |

| RWC | 0b | whether the mask bit is set in the advanced error capability) on either interface or internally. |

|

|

|

| The bit remains set until the software writes a 1 to clear it. |

|

|

|

|

|

|

|

|

| Detected Correctable Error: This bit is set when a correctable error is detected |

0 |

| RWC | 0b | (regardless of whether the mask bit is set in the advanced error capability) on either |

|

|

|

| interface or internally. The bit remains set until the software writes a 1 to clear it. |

|

|

|

|

|

12.2.30Offset 50h: EXP_LCAP—PCI Express* Link Capabilities Register

Table 64. | Offset 50h: | |||

|

|

|

|

|

Bits |

| Type | Default | Description |

|

|

|

|

|

31:24 |

| RO | 00h | Port Number: Not applicable |

|

|

|

|

|

23:18 |

| RsvdP | 00h | Preserved |

|

|

|

|

|

17:15 |

| RO | 111b | L1 Exit Latency: L1 transition is not supported. |

|

|

|

|

|

94 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |