In summary:

•A_RST# and B_RST# are outputs from the 41210.

•PCI clocks are actively driven out from the 41210.

•The 41210 drives X_AD[31:0], X_BE[3:0], and X_PAR low during PCI bus reset.

•The 41210 drives X_REQ64# low during reset.

3.2Transactions Supported

3.2.1PCI Mode

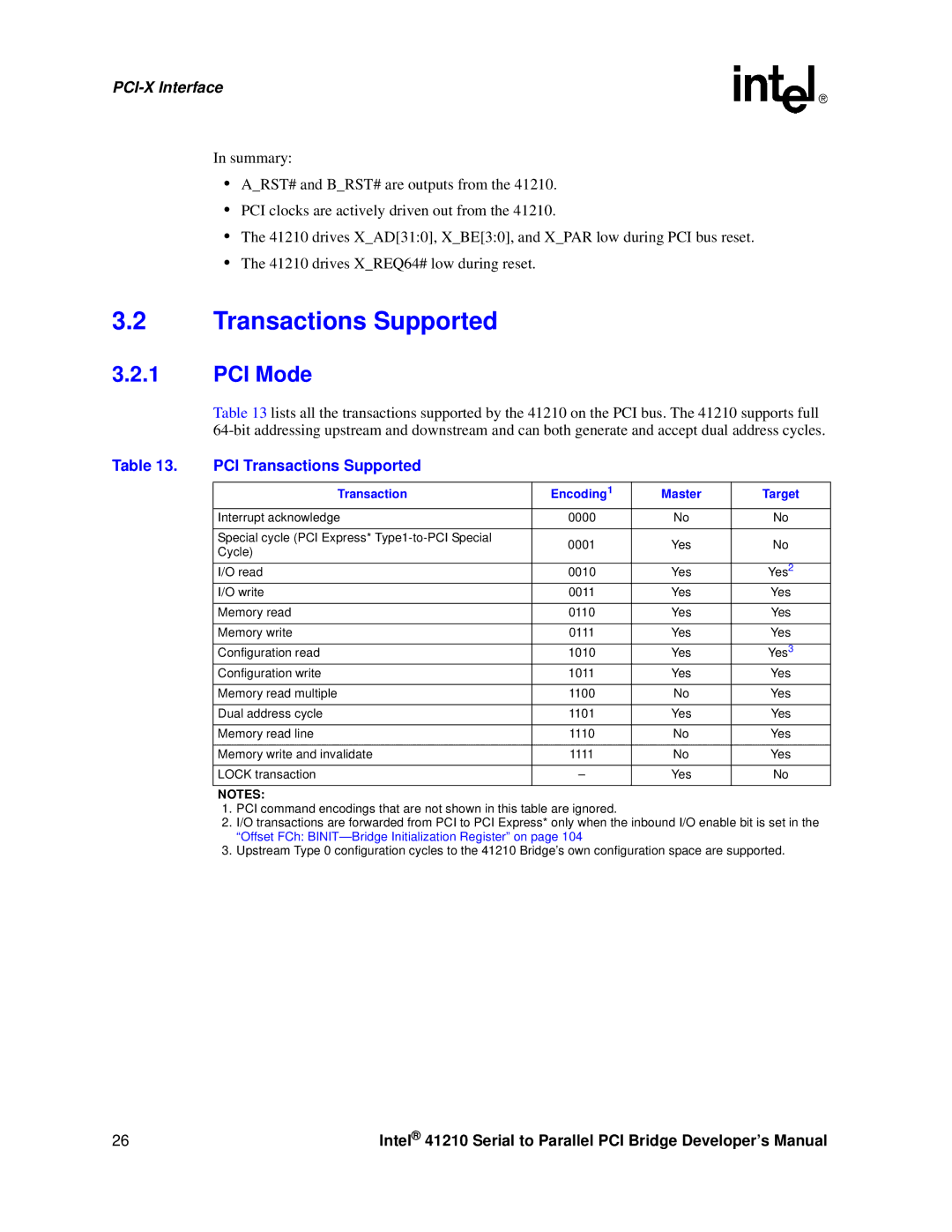

Table 13 lists all the transactions supported by the 41210 on the PCI bus. The 41210 supports full

Table 13. | PCI Transactions Supported |

|

|

|

|

|

|

|

|

| Transaction | Encoding1 | Master | Target |

| Interrupt acknowledge | 0000 | No | No |

|

|

|

|

|

| Special cycle (PCI Express* | 0001 | Yes | No |

| Cycle) | |||

|

|

|

| |

| I/O read | 0010 | Yes | Yes2 |

| I/O write | 0011 | Yes | Yes |

|

|

|

|

|

| Memory read | 0110 | Yes | Yes |

|

|

|

|

|

| Memory write | 0111 | Yes | Yes |

|

|

|

|

|

| Configuration read | 1010 | Yes | Yes3 |

| Configuration write | 1011 | Yes | Yes |

|

|

|

|

|

| Memory read multiple | 1100 | No | Yes |

|

|

|

|

|

| Dual address cycle | 1101 | Yes | Yes |

|

|

|

|

|

| Memory read line | 1110 | No | Yes |

|

|

|

|

|

| Memory write and invalidate | 1111 | No | Yes |

|

|

|

|

|

| LOCK transaction | – | Yes | No |

|

|

|

|

|

| NOTES: |

|

|

|

1.PCI command encodings that are not shown in this table are ignored.

2.I/O transactions are forwarded from PCI to PCI Express* only when the inbound I/O enable bit is set in the “Offset FCh:

3.Upstream Type 0 configuration cycles to the 41210 Bridge’s own configuration space are supported.

26 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |