Register Description

12.2.59Offset 12Ch:

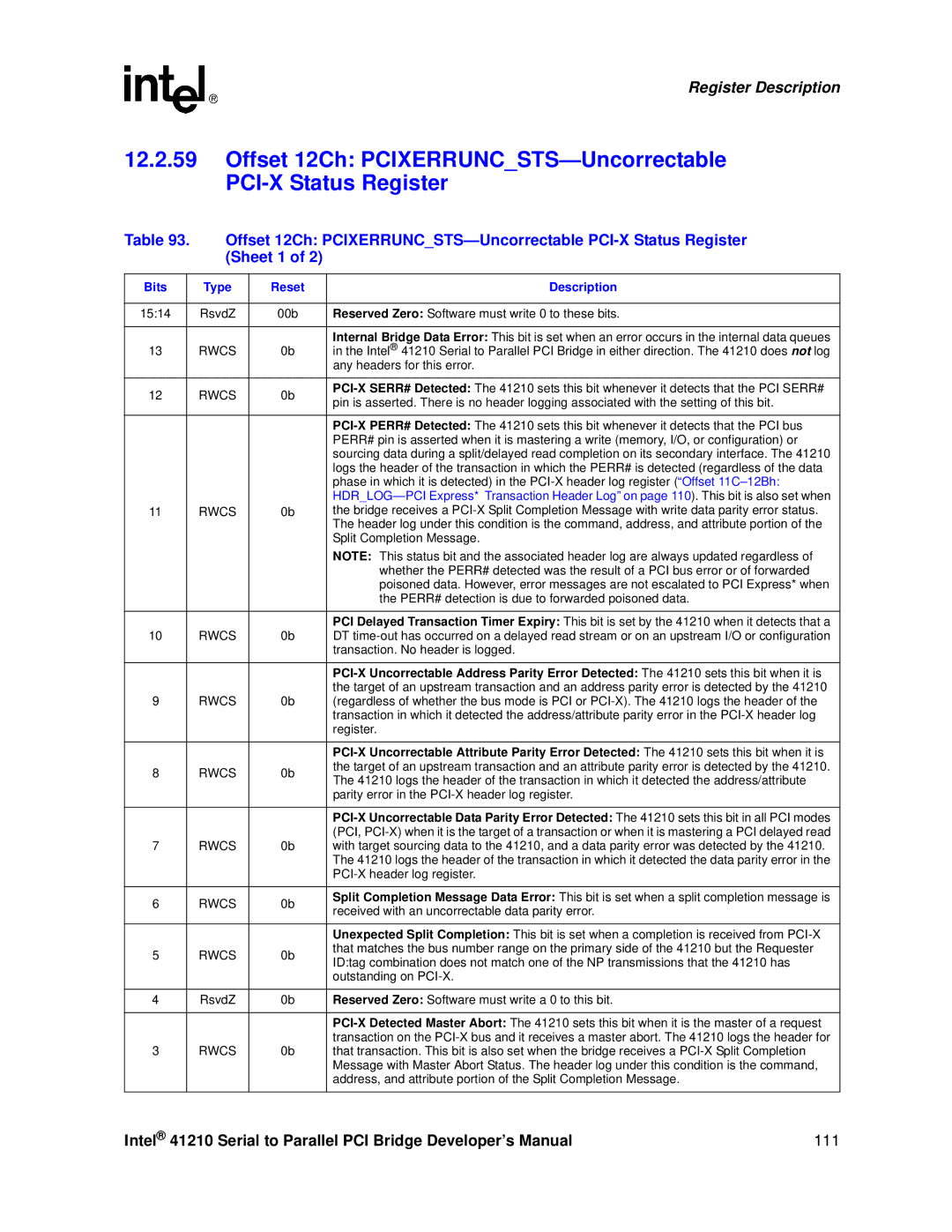

Table 93. | Offset 12Ch: | |||

|

| (Sheet 1 of 2) |

| |

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

15:14 |

| RsvdZ | 00b | Reserved Zero: Software must write 0 to these bits. |

|

|

|

|

|

|

|

|

| Internal Bridge Data Error: This bit is set when an error occurs in the internal data queues |

13 |

| RWCS | 0b | in the Intel® 41210 Serial to Parallel PCI Bridge in either direction. The 41210 does not log |

|

|

|

| any headers for this error. |

|

|

|

|

|

12 |

| RWCS | 0b | |

| pin is asserted. There is no header logging associated with the setting of this bit. | |||

|

|

|

| |

|

|

|

|

|

|

|

|

| |

|

|

|

| PERR# pin is asserted when it is mastering a write (memory, I/O, or configuration) or |

|

|

|

| sourcing data during a split/delayed read completion on its secondary interface. The 41210 |

|

|

|

| logs the header of the transaction in which the PERR# is detected (regardless of the data |

|

|

|

| phase in which it is detected) in the |

|

|

|

| |

11 |

| RWCS | 0b | the bridge receives a |

|

|

|

| The header log under this condition is the command, address, and attribute portion of the |

|

|

|

| Split Completion Message. |

|

|

|

| NOTE: This status bit and the associated header log are always updated regardless of |

|

|

|

| whether the PERR# detected was the result of a PCI bus error or of forwarded |

|

|

|

| poisoned data. However, error messages are not escalated to PCI Express* when |

|

|

|

| the PERR# detection is due to forwarded poisoned data. |

|

|

|

|

|

|

|

|

| PCI Delayed Transaction Timer Expiry: This bit is set by the 41210 when it detects that a |

10 |

| RWCS | 0b | DT |

|

|

|

| transaction. No header is logged. |

|

|

|

|

|

|

|

|

| |

|

|

|

| the target of an upstream transaction and an address parity error is detected by the 41210 |

9 |

| RWCS | 0b | (regardless of whether the bus mode is PCI or |

|

|

|

| transaction in which it detected the address/attribute parity error in the |

|

|

|

| register. |

|

|

|

|

|

|

|

|

| |

8 |

| RWCS | 0b | the target of an upstream transaction and an attribute parity error is detected by the 41210. |

| The 41210 logs the header of the transaction in which it detected the address/attribute | |||

|

|

|

| |

|

|

|

| parity error in the |

|

|

|

|

|

|

|

|

| |

|

|

|

| (PCI, |

7 |

| RWCS | 0b | with target sourcing data to the 41210, and a data parity error was detected by the 41210. |

|

|

|

| The 41210 logs the header of the transaction in which it detected the data parity error in the |

|

|

|

| |

|

|

|

|

|

6 |

| RWCS | 0b | Split Completion Message Data Error: This bit is set when a split completion message is |

| received with an uncorrectable data parity error. | |||

|

|

|

| |

|

|

|

|

|

|

|

|

| Unexpected Split Completion: This bit is set when a completion is received from |

5 |

| RWCS | 0b | that matches the bus number range on the primary side of the 41210 but the Requester |

| ID:tag combination does not match one of the NP transmissions that the 41210 has | |||

|

|

|

| |

|

|

|

| outstanding on |

|

|

|

|

|

4 |

| RsvdZ | 0b | Reserved Zero: Software must write a 0 to this bit. |

|

|

|

|

|

|

|

|

| |

3 |

| RWCS | 0b | transaction on the |

| that transaction. This bit is also set when the bridge receives a | |||

|

|

|

| Message with Master Abort Status. The header log under this condition is the command, |

|

|

|

| address, and attribute portion of the Split Completion Message. |

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 111 |