Addressing

5.2Secondary PCI Devices

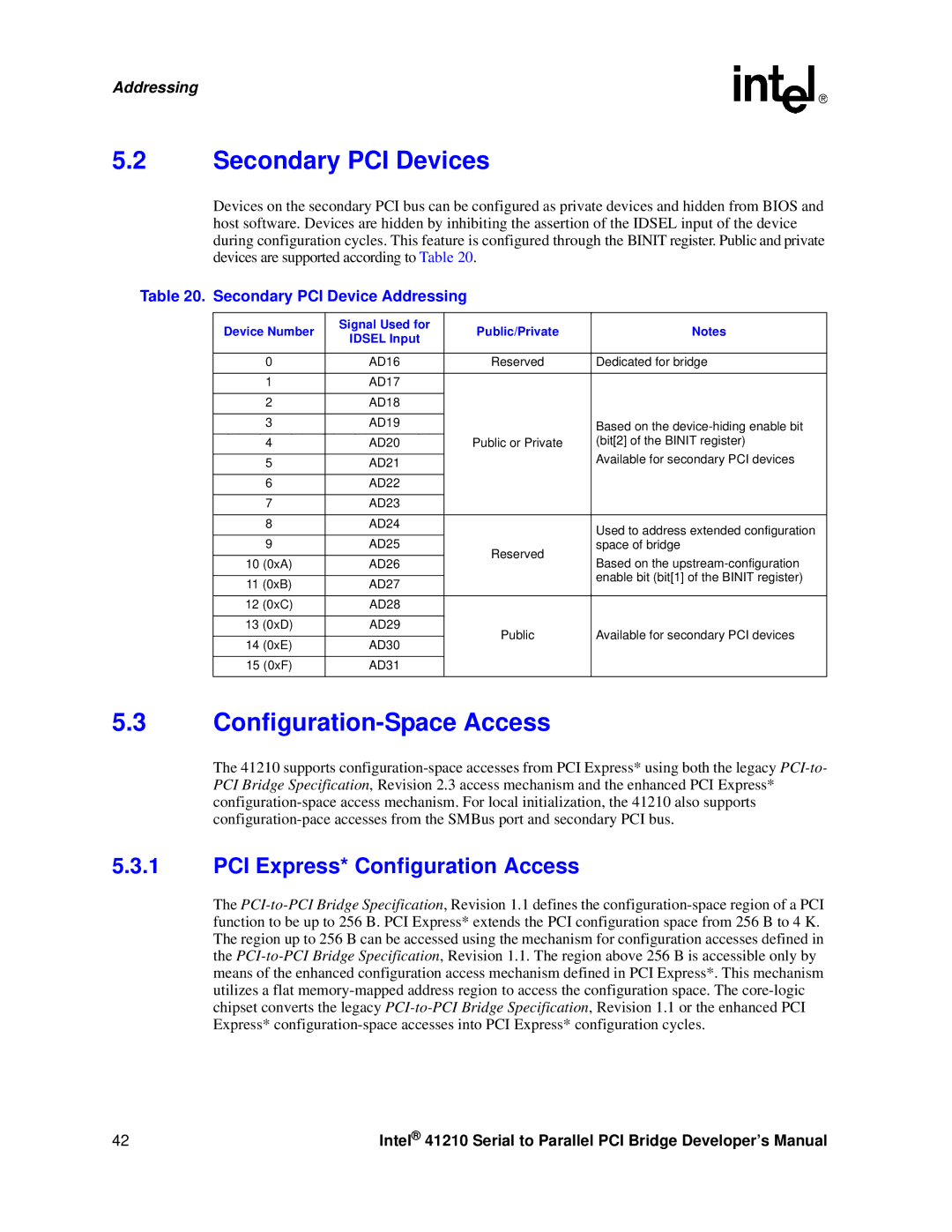

Devices on the secondary PCI bus can be configured as private devices and hidden from BIOS and host software. Devices are hidden by inhibiting the assertion of the IDSEL input of the device during configuration cycles. This feature is configured through the BINIT register. Public and private devices are supported according to Table 20.

Table 20. Secondary PCI Device Addressing

Device Number | Signal Used for | Public/Private | Notes | |

IDSEL Input | ||||

|

|

| ||

|

|

|

| |

0 | AD16 | Reserved | Dedicated for bridge | |

|

|

|

| |

1 | AD17 |

|

| |

|

|

|

| |

2 | AD18 |

|

| |

|

|

|

| |

3 | AD19 |

| Based on the | |

4 | AD20 | Public or Private | (bit[2] of the BINIT register) | |

|

|

| Available for secondary PCI devices | |

5 | AD21 |

| ||

|

|

|

| |

6 | AD22 |

|

| |

|

|

|

| |

7 | AD23 |

|

| |

|

|

|

| |

8 | AD24 |

| Used to address extended configuration | |

|

|

| ||

9 | AD25 | Reserved | space of bridge | |

|

| Based on the | ||

10 (0xA) | AD26 | |||

| ||||

|

|

| enable bit (bit[1] of the BINIT register) | |

11 (0xB) | AD27 |

| ||

|

| |||

|

|

|

| |

12 (0xC) | AD28 |

|

| |

|

|

|

| |

13 (0xD) | AD29 | Public | Available for secondary PCI devices | |

|

| |||

14 (0xE) | AD30 | |||

|

| |||

|

|

|

| |

15 (0xF) | AD31 |

|

| |

|

|

|

|

5.3Configuration-Space Access

The 41210 supports

5.3.1PCI Express* Configuration Access

The

42 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |