Register Description

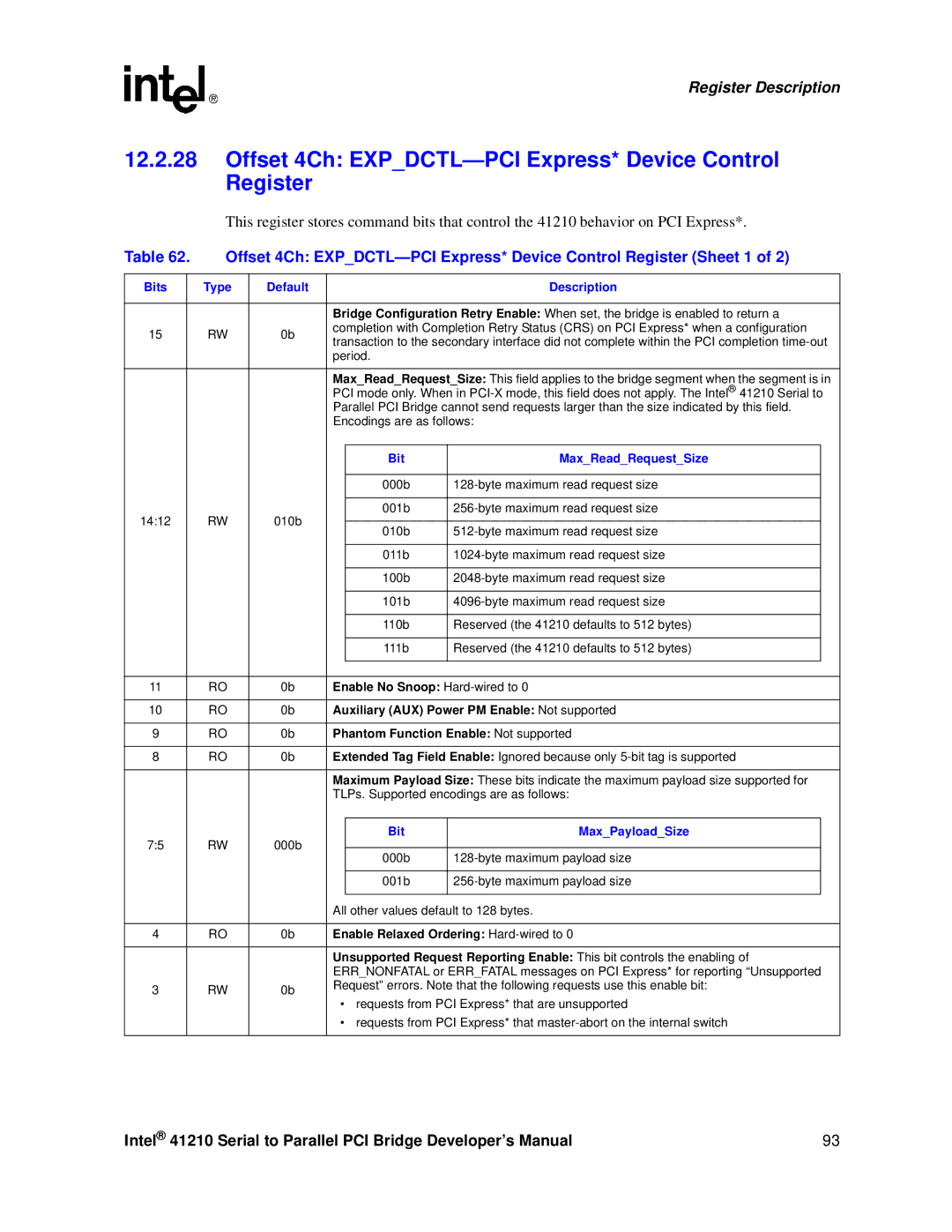

12.2.28Offset 4Ch: EXP_DCTL—PCI Express* Device Control Register

This register stores command bits that control the 41210 behavior on PCI Express*.

Table 62. | Offset 4Ch: | ||||||

|

|

|

|

|

|

|

|

Bits |

| Type | Default |

|

| Description | |

|

|

|

|

|

|

|

|

|

|

|

| Bridge Configuration Retry Enable: When set, the bridge is enabled to return a | |||

15 |

| RW | 0b | completion with Completion Retry Status (CRS) on PCI Express* when a configuration | |||

| transaction to the secondary interface did not complete within the PCI completion | ||||||

|

|

|

| ||||

|

|

|

| period. |

|

| |

|

|

|

|

|

|

|

|

|

|

|

| Max_Read_Request_Size: This field applies to the bridge segment when the segment is in | |||

|

|

|

| PCI mode only. When in | |||

|

|

|

| Parallel PCI Bridge cannot send requests larger than the size indicated by this field. | |||

|

|

|

| Encodings are as follows: | |||

|

|

|

|

|

|

|

|

|

|

|

|

| Bit | Max_Read_Request_Size |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 000b |

| |

|

|

|

|

|

|

|

|

14:12 |

| RW | 010b |

| 001b |

| |

|

|

|

|

| |||

|

| 010b |

| ||||

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

| 011b |

| |

|

|

|

|

|

|

|

|

|

|

|

|

| 100b |

| |

|

|

|

|

|

|

|

|

|

|

|

|

| 101b |

| |

|

|

|

|

|

|

|

|

|

|

|

|

| 110b | Reserved (the 41210 defaults to 512 bytes) |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 111b | Reserved (the 41210 defaults to 512 bytes) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

| RO | 0b | Enable No Snoop: | |||

|

|

|

|

|

|

|

|

10 |

| RO | 0b | Auxiliary (AUX) Power PM Enable: Not supported | |||

|

|

|

|

|

|

|

|

9 |

| RO | 0b | Phantom Function Enable: Not supported | |||

|

|

|

|

|

|

|

|

8 |

| RO | 0b | Extended Tag Field Enable: Ignored because only | |||

|

|

|

|

|

|

|

|

|

|

|

| Maximum Payload Size: These bits indicate the maximum payload size supported for | |||

|

|

|

| TLPs. Supported encodings are as follows: | |||

|

|

|

|

|

|

| |

7:5 |

| RW | 000b |

| Bit | Max_Payload_Size |

|

|

|

|

|

| |||

|

| 000b |

| ||||

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

| 001b |

| |

|

|

|

|

|

|

|

|

|

|

|

| All other values default to 128 bytes. | |||

|

|

|

|

|

|

|

|

4 |

| RO | 0b | Enable Relaxed Ordering: | |||

|

|

|

|

|

|

|

|

|

|

|

| Unsupported Request Reporting Enable: This bit controls the enabling of | |||

|

|

|

| ERR_NONFATAL or ERR_FATAL messages on PCI Express* for reporting “Unsupported | |||

3 |

| RW | 0b | Request” errors. Note that the following requests use this enable bit: | |||

| • requests from PCI Express* that are unsupported | ||||||

|

|

|

| ||||

|

|

|

| • requests from PCI Express* that | |||

|

|

|

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 93 |