Addressing

5.5.1Memory-Mapped I/O Window

Software uses the

The

1 MB.

This range is defined by a

Note: Setting the base to a value greater than that of the limit turns off the memory range.

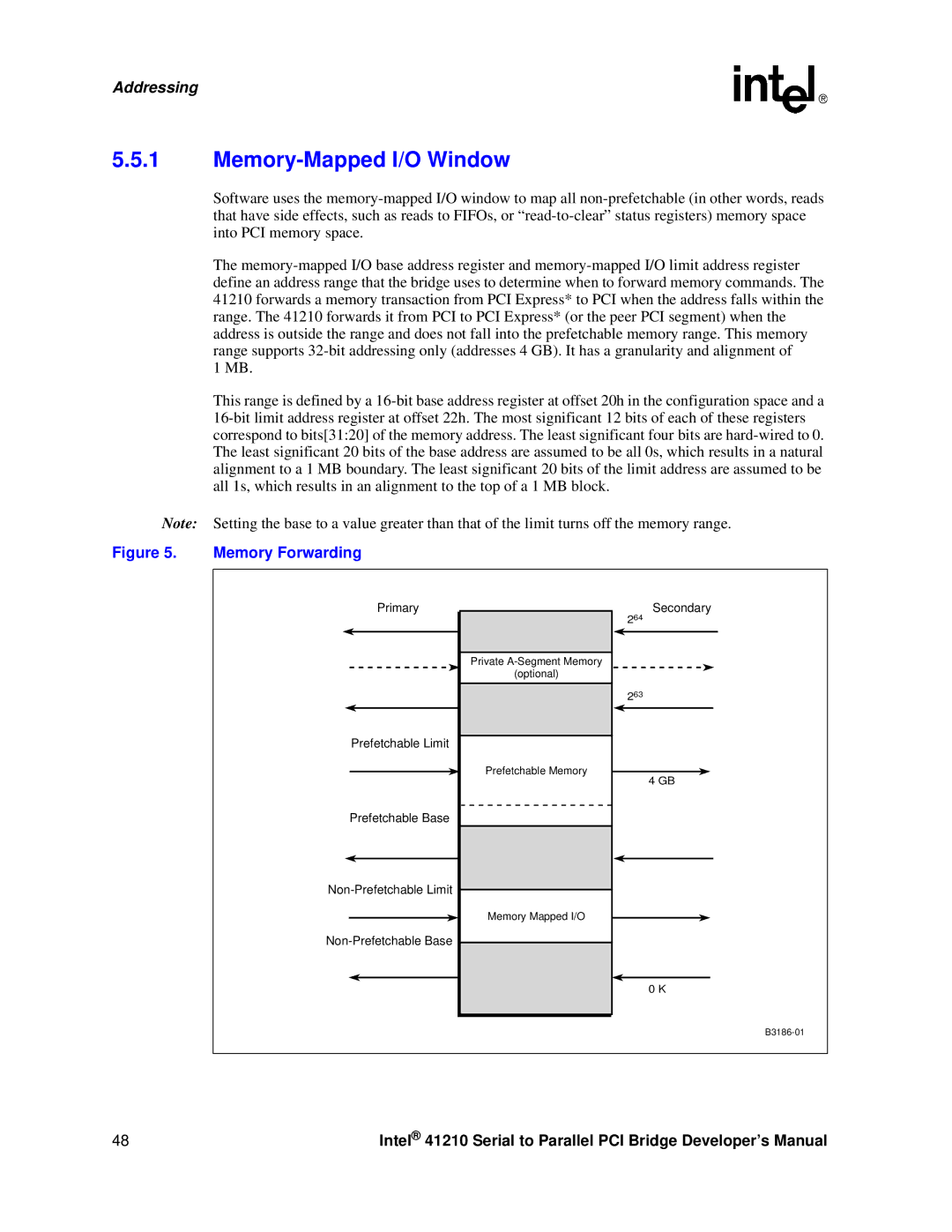

Figure 5. Memory Forwarding

Primary

Prefetchable Limit

Prefetchable Base

Private

(optional)

Prefetchable Memory

Memory Mapped I/O

Secondary

264

263

4 GB

0 K

48 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |