Register Description |

|

|

| |||

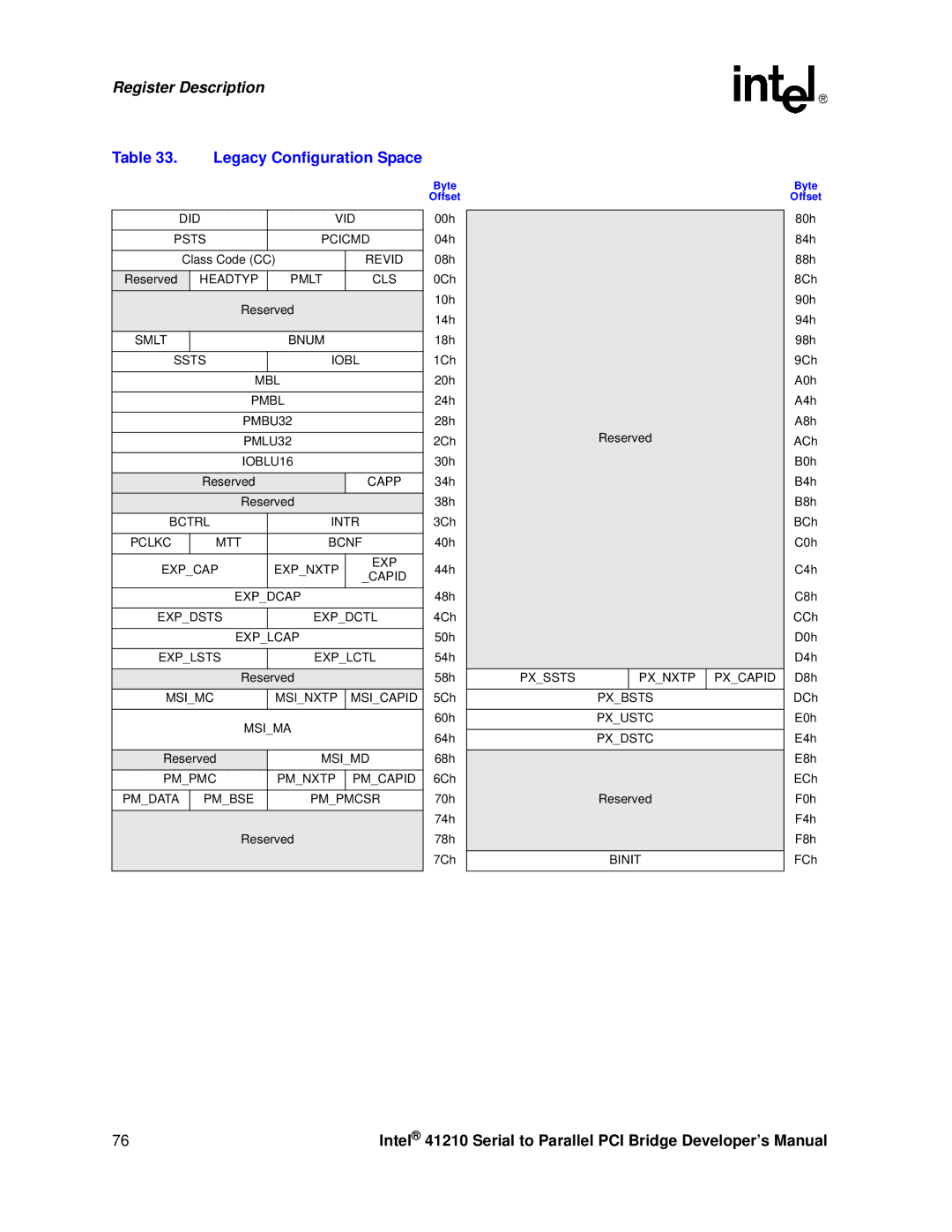

Table 33. |

| Legacy Configuration Space |

| |||

|

|

|

|

| Byte | |

|

|

|

|

| Offset | |

|

|

|

| 00h | ||

DID | VID | |||||

|

| 04h | ||||

PSTS | PCICMD | |||||

|

|

|

| 08h | ||

| Class Code (CC) | REVID | ||||

|

|

|

|

| 0Ch | |

Reserved |

| HEADTYP | PMLT | CLS | ||

|

| Reserved |

| 10h | ||

|

|

| 14h | |||

|

|

|

|

| ||

SMLT |

|

| BNUM |

| 18h | |

|

|

|

| 1Ch | ||

SSTS | IOBL | |||||

|

|

|

|

| 20h | |

|

| MBL |

| |||

|

|

|

| 24h | ||

|

| PMBL |

| |||

|

|

|

| 28h | ||

|

| PMBU32 |

| |||

|

|

|

| 2Ch | ||

|

| PMLU32 |

| |||

|

|

|

| 30h | ||

|

| IOBLU16 |

| |||

|

|

|

|

| 34h | |

|

| Reserved |

| CAPP | ||

|

| Reserved |

| 38h | ||

BCTRL | INTR | 3Ch | ||||

|

|

|

|

| 40h | |

PCLKC |

| MTT | BCNF | |||

|

|

|

|

|

| |

EXP_CAP | EXP_NXTP | EXP | 44h | |||

_CAPID | ||||||

|

|

|

|

| ||

|

|

|

|

| 48h | |

|

| EXP_DCAP |

| |||

|

|

| 4Ch | |||

EXP_DSTS | EXP_DCTL | |||||

|

|

|

|

| 50h | |

|

| EXP_LCAP |

| |||

|

|

| 54h | |||

EXP_LSTS | EXP_LCTL | |||||

|

|

|

|

| 58h | |

|

| Reserved |

| |||

MSI_MC | MSI_NXTP | MSI_CAPID | 5Ch | |||

|

|

|

|

| 60h | |

|

| MSI_MA |

| |||

|

|

| 64h | |||

|

|

|

|

| ||

|

|

|

| 68h | ||

Reserved | MSI_MD | |||||

PM_PMC | PM_NXTP | PM_CAPID | 6Ch | |||

|

|

|

|

| 70h | |

PM_DATA |

| PM_BSE | PM_PMCSR | |||

|

|

|

|

| 74h | |

|

|

|

|

| ||

|

| Reserved |

| 78h | ||

|

|

|

|

| 7Ch | |

|

|

|

|

|

| |

Reserved

PX_SSTS |

| PX_NXTP | PX_CAPID |

|

|

|

|

| PX_BSTS | ||

|

| ||

| PX_USTC | ||

|

| ||

| PX_DSTC | ||

|

|

|

|

| Reserved | ||

|

|

|

|

| BINIT | ||

Byte

Offset

80h

84h

88h

8Ch

90h

94h

98h

9Ch

A0h

A4h

A8h ACh B0h B4h B8h BCh C0h

C4h

C8h

CCh

D0h

D4h

D8h

DCh

E0h

E4h

E8h

ECh

F0h

F4h

F8h

FCh

76 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |