PCI-X Interface

3.3.4Split Transactions

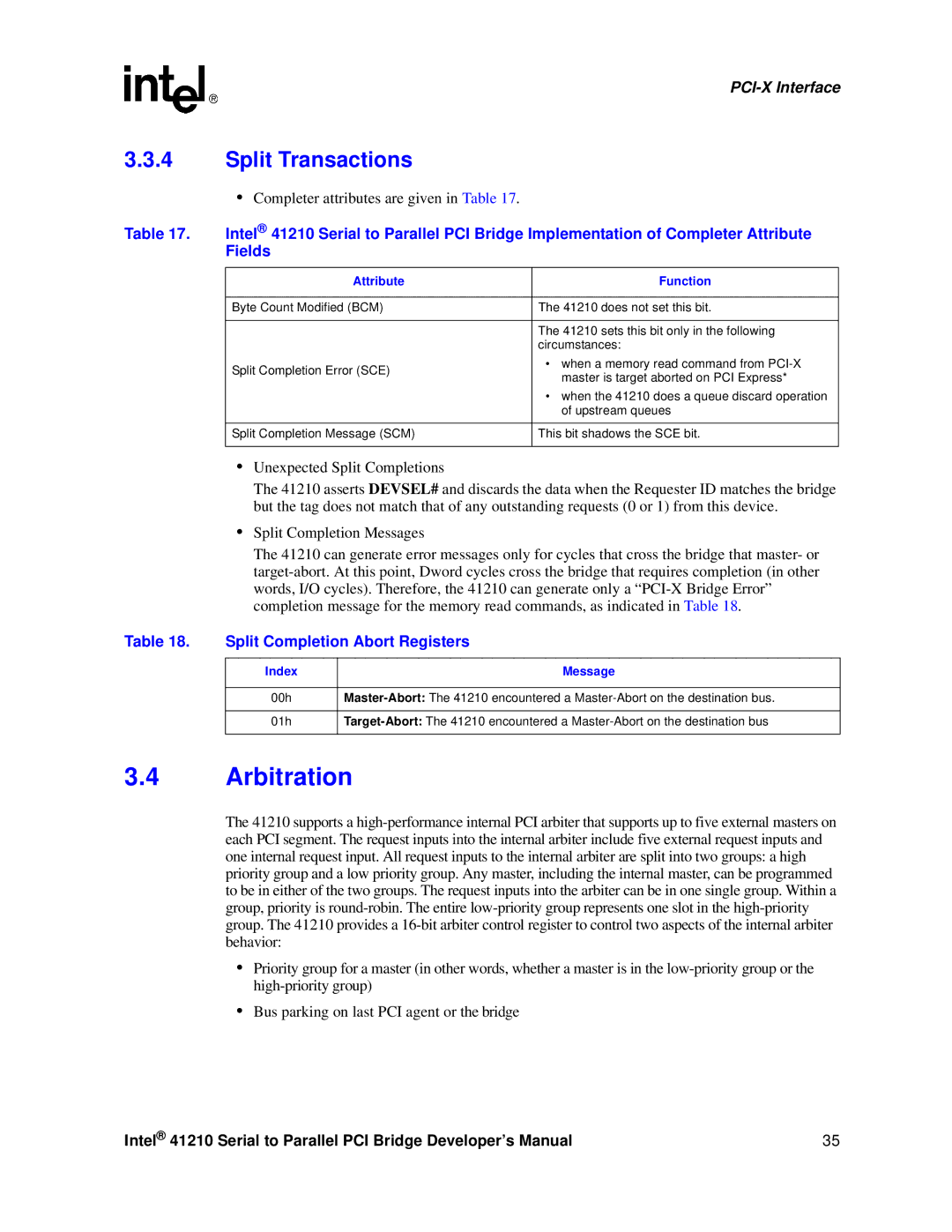

| • Completer attributes are given in Table 17. |

|

Table 17. | Intel® 41210 Serial to Parallel PCI Bridge Implementation of Completer Attribute | |

| Fields |

|

|

|

|

| Attribute | Function |

|

|

|

| Byte Count Modified (BCM) | The 41210 does not set this bit. |

|

|

|

|

| The 41210 sets this bit only in the following |

|

| circumstances: |

| Split Completion Error (SCE) | • when a memory read command from |

| master is target aborted on PCI Express* | |

|

| |

|

| • when the 41210 does a queue discard operation |

|

| of upstream queues |

|

|

|

| Split Completion Message (SCM) | This bit shadows the SCE bit. |

|

|

|

•Unexpected Split Completions

The 41210 asserts DEVSEL# and discards the data when the Requester ID matches the bridge but the tag does not match that of any outstanding requests (0 or 1) from this device.

•Split Completion Messages

The 41210 can generate error messages only for cycles that cross the bridge that master- or

Table 18. | Split Completion Abort Registers | |

|

|

|

| Index | Message |

|

|

|

| 00h | |

|

|

|

| 01h | |

|

|

|

3.4Arbitration

The 41210 supports a

•Priority group for a master (in other words, whether a master is in the

•Bus parking on last PCI agent or the bridge

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 35 |