Register Description

12.2.49Offset E4h: PX_DSTC—PCI-X Downstream Split Transaction Control

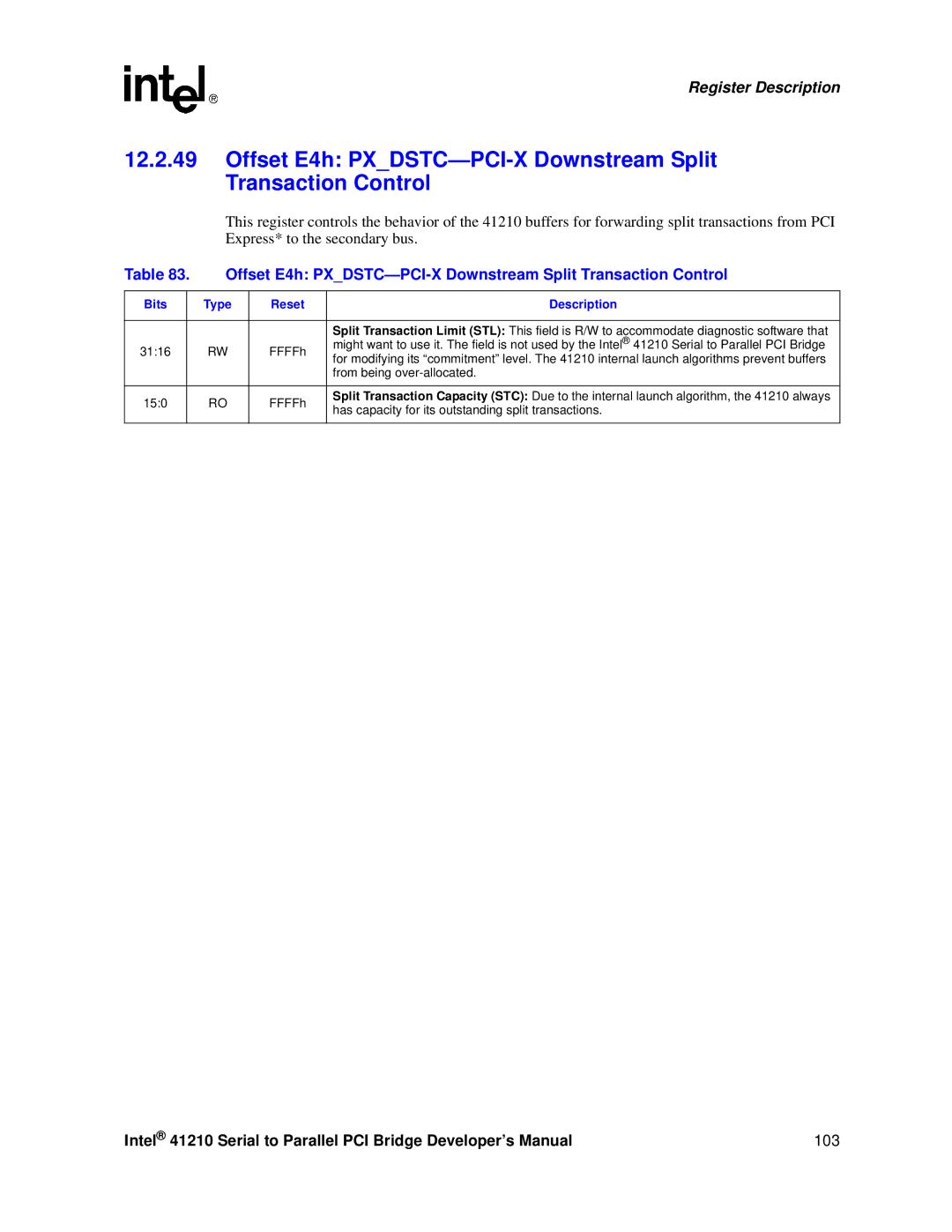

This register controls the behavior of the 41210 buffers for forwarding split transactions from PCI Express* to the secondary bus.

Table 83. | Offset E4h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

|

|

|

| Split Transaction Limit (STL): This field is R/W to accommodate diagnostic software that |

31:16 |

| RW | FFFFh | might want to use it. The field is not used by the Intel® 41210 Serial to Parallel PCI Bridge |

| for modifying its “commitment” level. The 41210 internal launch algorithms prevent buffers | |||

|

|

|

| |

|

|

|

| from being |

|

|

|

|

|

15:0 |

| RO | FFFFh | Split Transaction Capacity (STC): Due to the internal launch algorithm, the 41210 always |

| has capacity for its outstanding split transactions. | |||

|

|

|

| |

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 103 |