System Management Bus Interface

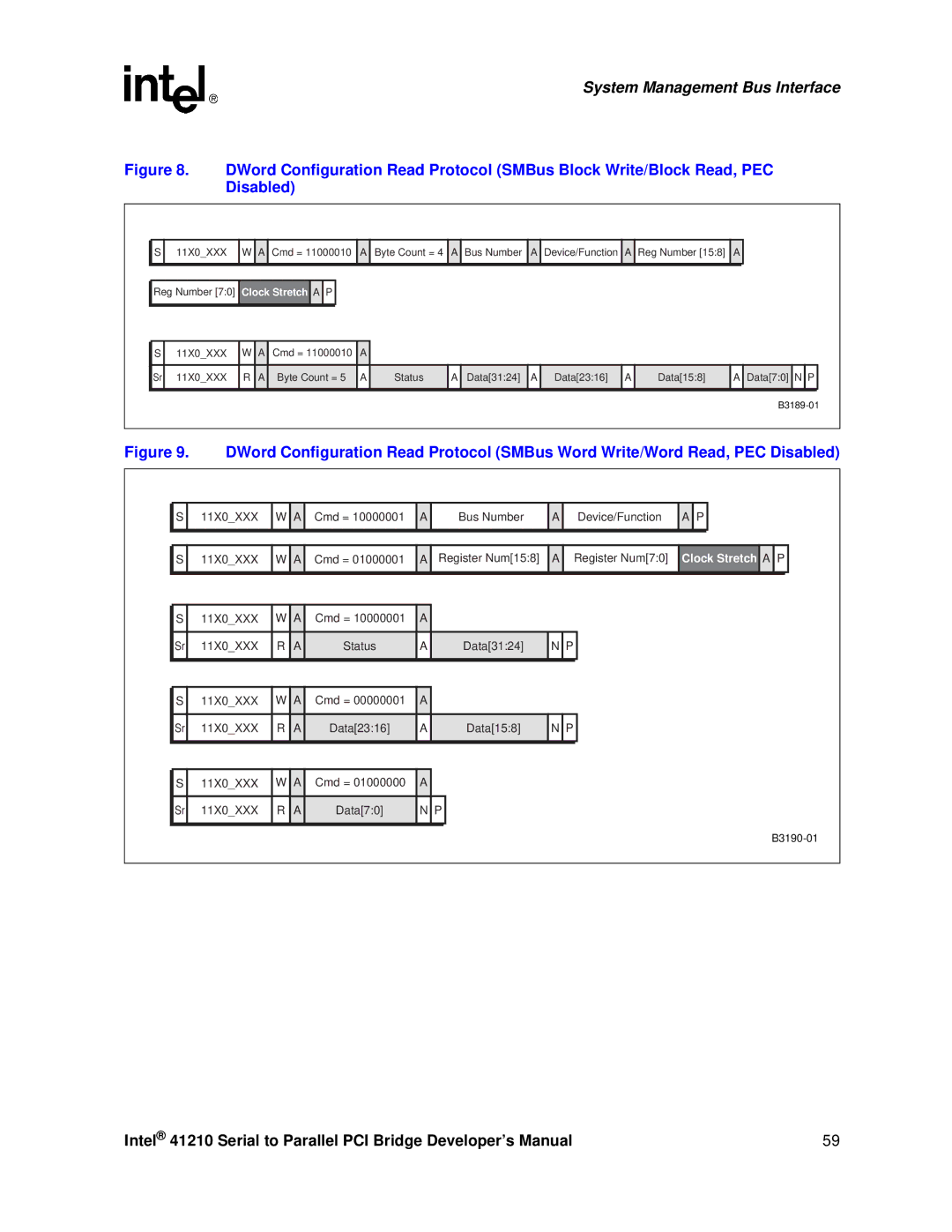

Figure 8. DWord Configuration Read Protocol (SMBus Block Write/Block Read, PEC Disabled)

S

11X0_XXX

W A Cmd = 11000010 A Byte Count = 4 A Bus Number A Device/Function A Reg Number [15:8] A

Reg Number [7:0]

Clock Stretch

A P

S | 11X0_XXX | W | A | Cmd = 11000010 | A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Sr | 11X0_XXX | R | A | Byte Count = 5 | A | Status | A | Data[31:24] | A | Data[23:16] | A | Data[15:8] | A | Data[7:0] | N | P |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

Figure 9. DWord Configuration Read Protocol (SMBus Word Write/Word Read, PEC Disabled)

S 11X0_XXX

W A

Cmd = 10000001

A

Bus Number

A

Device/Function

A P

S 11X0_XXX

W A

Cmd = 01000001

A

Register Num[15:8]

A

Register Num[7:0]

Clock Stretch

A P

| S | 11X0_XXX | W | A | Cmd = 10000001 | A |

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| Sr | 11X0_XXX | R | A | Status | A |

| Data[31:24] | N | P |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| S | 11X0_XXX | W | A | Cmd = 00000001 | A |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| Sr | 11X0_XXX | R | A | Data[23:16] | A |

| Data[15:8] | N | P |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| S | 11X0_XXX | W | A | Cmd = 01000000 | A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Sr | 11X0_XXX | R | A | Data[7:0] | N | P |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual | 59 |