Register Description

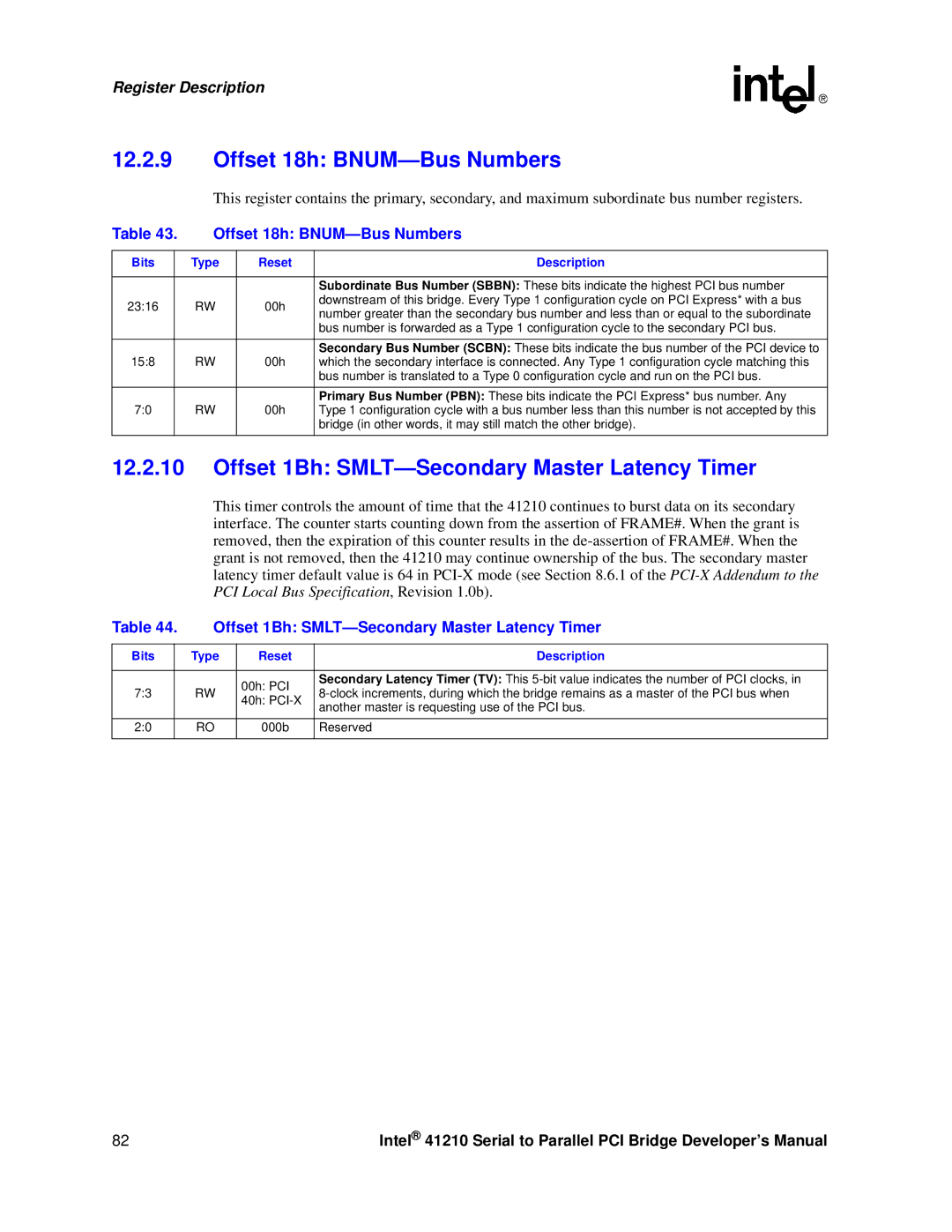

12.2.9Offset 18h: BNUM—Bus Numbers

This register contains the primary, secondary, and maximum subordinate bus number registers.

Table 43. | Offset 18h: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

|

|

|

| Subordinate Bus Number (SBBN): These bits indicate the highest PCI bus number |

23:16 |

| RW | 00h | downstream of this bridge. Every Type 1 configuration cycle on PCI Express* with a bus |

| number greater than the secondary bus number and less than or equal to the subordinate | |||

|

|

|

| |

|

|

|

| bus number is forwarded as a Type 1 configuration cycle to the secondary PCI bus. |

|

|

|

|

|

|

|

|

| Secondary Bus Number (SCBN): These bits indicate the bus number of the PCI device to |

15:8 |

| RW | 00h | which the secondary interface is connected. Any Type 1 configuration cycle matching this |

|

|

|

| bus number is translated to a Type 0 configuration cycle and run on the PCI bus. |

|

|

|

|

|

|

|

|

| Primary Bus Number (PBN): These bits indicate the PCI Express* bus number. Any |

7:0 |

| RW | 00h | Type 1 configuration cycle with a bus number less than this number is not accepted by this |

|

|

|

| bridge (in other words, it may still match the other bridge). |

|

|

|

|

|

12.2.10Offset 1Bh: SMLT—Secondary Master Latency Timer

This timer controls the amount of time that the 41210 continues to burst data on its secondary interface. The counter starts counting down from the assertion of FRAME#. When the grant is removed, then the expiration of this counter results in the

Table 44. | Offset 1Bh: | |||

|

|

|

|

|

Bits |

| Type | Reset | Description |

|

|

|

|

|

7:3 |

| RW | 00h: PCI | Secondary Latency Timer (TV): This |

| ||||

| 40h: | |||

|

|

| another master is requesting use of the PCI bus. | |

|

|

|

| |

|

|

|

|

|

2:0 |

| RO | 000b | Reserved |

|

|

|

|

|

82 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |