PCI-X Interface

3.3PCI-X Protocol Specifics

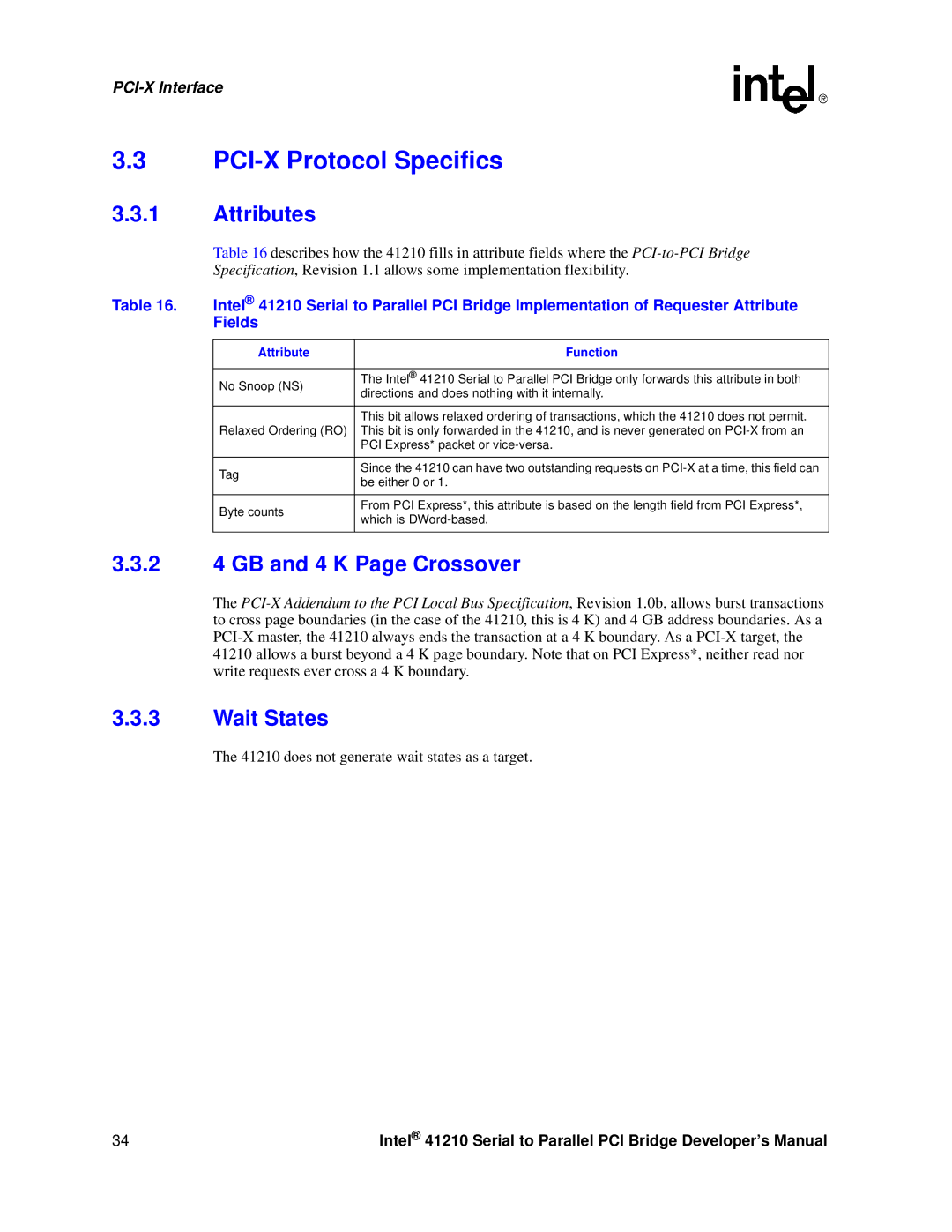

3.3.1Attributes

Table 16 describes how the 41210 fills in attribute fields where the

Specification, Revision 1.1 allows some implementation flexibility.

Table 16. Intel® 41210 Serial to Parallel PCI Bridge Implementation of Requester Attribute Fields

Attribute | Function | |

|

| |

No Snoop (NS) | The Intel® 41210 Serial to Parallel PCI Bridge only forwards this attribute in both | |

directions and does nothing with it internally. | ||

| ||

|

| |

| This bit allows relaxed ordering of transactions, which the 41210 does not permit. | |

Relaxed Ordering (RO) | This bit is only forwarded in the 41210, and is never generated on | |

| PCI Express* packet or | |

|

| |

Tag | Since the 41210 can have two outstanding requests on | |

be either 0 or 1. | ||

| ||

|

| |

Byte counts | From PCI Express*, this attribute is based on the length field from PCI Express*, | |

which is | ||

| ||

|

|

3.3.24 GB and 4 K Page Crossover

The

3.3.3Wait States

The 41210 does not generate wait states as a target.

34 | Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual |