80C186XL/80C188XL Microprocessor User’s Manual

80C186XL/80C188XL Microprocessor User’s Manual

Intel Corporation

Contents

Contents

Setting the PCB Base Location

Power Management

Clock Generation

LCS

Chapter Refresh Control Unit

Programming the Interrupt Control Unit

Functional Overview Programming the TIMER/COUNTER Unit

Functional Overview

Chapter Math Coprocessing

Chapter Once Mode

Figures

Reset Configuration

UCS

Interrupt Control Register for Noncascadable External Pins

10-9

Tables

Flag Bit Functions

Examples

Example

Introduction

Page

Chapter Introduction

Feature 80C186XL 80C186EA 80C186EB 80C186EC

HOW to USE this Manual

Comparison of 80C186 Modular Core Family Products

Related Documents and Software

Related Documents

Document/Software Title Order No

FaxBack Service

Electronic Support Systems

Bulletin Board System BBS

World Wide Web

CompuServe Forums

Technical Support

Product Literature

Training Classes

Page

Overview 80C186 Family Architecture

Page

Chapter Overview of the 80C186 Family Architecture

Architectural Overview

Simplified Functional Block Diagram of the 80C186 Family CPU

Execution Unit

Bus Interface Unit

Physical Address Generation

General Registers

General Registers

Implicit Use of General Registers

Segment Registers

Operations

Instruction Pointer

Segment Registers

Flags

Memory Segmentation

Register Name

Register Mnemonic

PSW Flags

Register Function

Logical Addresses

Segment Locations in Physical Memory

Data DS Code CS Stack SS Extra ES

Fffffh

2BFH 2BEH 2BDH 2BCH 2BBH 2BAH

Dynamically Relocatable Code

Type of Memory Reference Default Alternate Offset

Logical Address Sources

Segment Code Data

Before After Relocation Code Segment

Segment Data Extra

Stack Implementation

Reserved Memory and I/O Space

10. Stack Operation

Software Overview

Instruction Set

General-Purpose

Data Transfer Instructions

Input/Output

Lahf S Z U a U P U C

Sahf 7 6 5 4 3 2 1

Pushf Popf U U O D I T S Z U a U P U C

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

Addition

Subtraction

Multiplication

Division

Arithmetic Interpretation of 8-Bit Numbers

Bit Manipulation Instructions

Hex Bit Pattern Unsigned Signed Unpacked Packed Binary

Shifts

String Instructions

Program Transfer Instructions

String Instruction Register and Flag Use

CX AL/AX

Overview of the 80C186 Family Architecture

Conditional Transfers

Unconditional Transfers

Iteration Control

Interrupts

10. Interpretation of Conditional Transfers

Mnemonic Condition Tested Jump if…

Addressing Modes

Processor Control Instructions

11. Processor Control Instructions

Register and Immediate Operand Addressing Modes

Memory Addressing Modes

0000 Physical Addr

BIU

Opcode Mod R/M Displacement

13. Direct Addressing

14. Register Indirect Addressing

15. Based Addressing

Displacement High Address Rate Age

Rate Base Vac

Base Register

Register Dept Div Employee Age

18. Accessing an Array with Indexed Addressing

17. Indexed Addressing

19. Based Index Addressing

20. Accessing a Stacked Array with Based Index Addressing

Opcode Source EA Destination EA

Data Types Used in the 80C186 Modular Core Family

12. Supported Data Types

Type Description

BCD

23 C186 Modular Core Family Supported Data Types

Interrupts and Exception Handling

Interrupt/Exception Processing

3FE

3FC

Overview of the 80C186 Family Architecture

Interrupt Enable Bit

Stack

PSW

Trap Flag

Maskable Interrupts

Exceptions

Invalid Opcode Type

Software Interrupts

Interrupt Latency

Interrupt Response Time

Clocks

Total

Interrupt and Exception Priority

NMI

Execute Divide Service Routine

Iret

Trap Flag = ???

29. Simultaneous NMI and Single Step Interrupts

Interrupt Enable Bit IE = Trap Flag TF =

30. Simultaneous NMI, Single Step and Maskable Interrupt

Page

Bus Interface Unit

Page

Address and Data BUS Concepts

Multiplexed Address and Data BUS

1 16-Bit Data Bus

Physical Implementation Address Space for

MByte KBytes

Fffff Ffffe Ffffd Ffffc

A190 D70 A191 D158

Even Byte Transfer

A191 D158 BHE High

Odd Byte Transfer

D70 A0 Low A191 D158 BHE High

A191 D158 BHE Low D70 A0 Low

Bit Data Bus Even Word Transfers

First Bus Cycle

A191 D158 BHE Low

Second Bus Cycle

D70 A0 High A191 D158 BHE Low

Memory and I/O Interfaces

Bit Data Bus Word Transfers

2 8-Bit Bus Memory and I/O Requirements

1 16-Bit Bus Memory and I/O Requirements

BUS Cycle Operation

Phase

Low Phase High Phase

Clkout ALE

S20 Valid Status AD150 Address Data

Bus Ready

Request Pending

Hold Deasserted

RES#

Address Status Phase Or TW Or TI Data Phase

Address/Status Phase

Or TI

Clkout

A1916

S20

STB

ALE STB

Data Phase

Wait States

Clkout RD/ WR

Or TW Or TI

AD150 Valid Write Data Read Read Data S20

Ardy Clkout Srdy

Ready

BUS Ready

CS1 CS2 CS3 CS4 ALE Clkout

16. Generating a Normally Ready Bus Signal

Clock

Clkout Ardy Srdy

Idle States

18. Normally Ready System Timings

BUS Cycles

Read Bus Cycles

Read Bus Cycle Types

Read Cycle Critical Timing Parameters

A158

Rfsh

A150

DT/R DEN

UCS

AD70 O0-7

27C256

LA151 AD158

Write Bus Cycle Types

A158 A150

Status Bits Bus Cycle Type

LA151

LA0 BHE

A014 O18 CS1 AD70 AD158

LCS

Interrupt Acknowledge Bus Cycle

Write Cycle Critical Timing Parameters

Lock DT/R DEN

INTA0 INTA1

BHE RD, WR

INTA0 Inta INT0 IR0 IR7 PCS0 LA1

Processor 82C59A

System Design Considerations

Halt Bus Cycle

Pins Pin State

011 AD150 AD70 A158 A1916

Rfsh =

BHE

Temporarily Exiting the Halt Bus State

Clkout Hold Hlda

AD150 AD70 A158 A1916

Control

S20 AD150 AD70 A158 A1916

BHE Rfsh

T4 T1 T2 T3

T3 TI TI TI TI

AD70 A158

RFSH=1

NMI/INTx

System Design Alternatives

Buffering the Data Bus

Clkout RD,WR DT/R DEN

DT/ R

Device

CPU Local Bus Buffered Bus

MCS0

Buffer Buffered Data Bus AD70

Buffer Local Data Bus

Synchronizing Software and Hardware Events

Using a Locked Bus

Using the Queue Status Signals

Queue Status Signal Decoding

Queue Status

No queue operation occurred

MULTI-MASTER BUS System Designs

Entering Bus Hold

Signal Hold Condition

Float

RD, W R Float BHE , S20

Lock

Refresh Operation During a Bus Hold

BHE, S20

Clkout Hold Hlda DEN RD, WR

DT/R Lock

Latched Hlda

Hlda Reset Hold PRE CLR

Exiting Hold

DT/R, S20 A1916, Lock

DEN RD, WR, BHE

BUS Cycle Priorities

BUS Interface Unit

Page

Peripheral Control Block

Page

Peripheral Control Registers

PCB Relocation Register

Register Name PCB Relocation Register Register Mnemonic

Bit Bit Name Reset Function Mnemonic State

Relreg

Peripheral Control Block

Accessing the Peripheral Control Block

Ready Signals and Wait States

Reserved Locations

Bus Cycles

Bus Operation

Word reads

Setting the PCB Base Location

Accessing the Peripheral Control Registers

Accessing Reserved Locations

Writing the PCB Relocation Register

Considerations for the 80C187 Math Coprocessor Interface

Page

Clock Generation Power Management

Page

RES

Clock Generation

Crystal Oscillator

= Inverter Output Z 90˚ 180˚

Oscillator Operation

Crystal Connections to Microprocessor

Third-Overtone Crystal Inductor L1

Values µH

Selecting Crystals

Reset and Clock Synchronization

Using an External Oscillator

Output from the Clock Generator

Typical Ct = V 1 e

1µf typical

Cold Reset Waveform

PCS60,NCS

Clkout

Power Management

Clkout Reset

RES Resync

Power-Save Mode

Entering Power-Save Mode

Power Save Register

Enables and sets clock division factor

Register Name Register Mnemonic Register Function

Pwrsav

10. Power-Save Clock Transition Leaving Power-Save Mode

Example Power-Save Initialization Code

Syntax

Chip-Select Unit

Page

CHIP-SELECT Unit Features and Benefits

Common Methods for Generating CHIP-SELECTS

Chip-Selects Using Addresses Directly Simple Decoder

CHIP-SELECT Unit Functional Overview

27C256

74AC138

MCS3

MCS2

MCS1

PCS1

A1916 UCS, PC S60

MCS30, LCS

1Address

Srdy Ardy UCS

Data Active For Top 1 KByte Memory Map

1MB

Programming

Initialization Sequence

Chip-Select Unit Registers

Control Register Alternate Register

Umcs

UCS Control Register

Controls the operation Chip-select

LCS Control Register

Lmcs

MCS Control Register

Mmcs

Controls the operation Chip-selects

MCS

Pacs

PCS Control Register

PCS

Mpcs

Register NameMCS and PCS Alternate Control Register

X S

Programming the Active Ranges

UCS Active Range

UCS Block Size and Starting Address

Umcs Field Block Size Starting Address U1710

LCS Active Range

LCS Active Range

MCS Active Range

Lmcs Field Block Size Ending Address U1710

MCS Block Size and Start Address Restrictions

Block Size Mmcs Start Address Kbytes Restrictions

Bus Wait State and Ready Control

PCS Active Range

Wait State Ready

R2 Control Bit Wait Wait State Value R10 State Counter

Overlapping Chip-Selects

Memory or I/O Bus Cycle Decoding

Programming Considerations

CHIP-SELECTS and BUS Hold

Example 1 Typical System Configuration

Examples

13. Typical System

Example 6-1. Initializing the Chip-Select Unit

MOD186XREF Name CSUEXAMPLE1

Drambase EQU

Place memory variables here

Refresh Control Unit

Page

CPU

CLR REQ

Refresh Control Unit Capabilities

Role of the Refresh Control Unit

Refresh Control Unit Operation

Refresh Control Unit Operation Flow Chart

Refresh Addresses

Refresh Address Formation

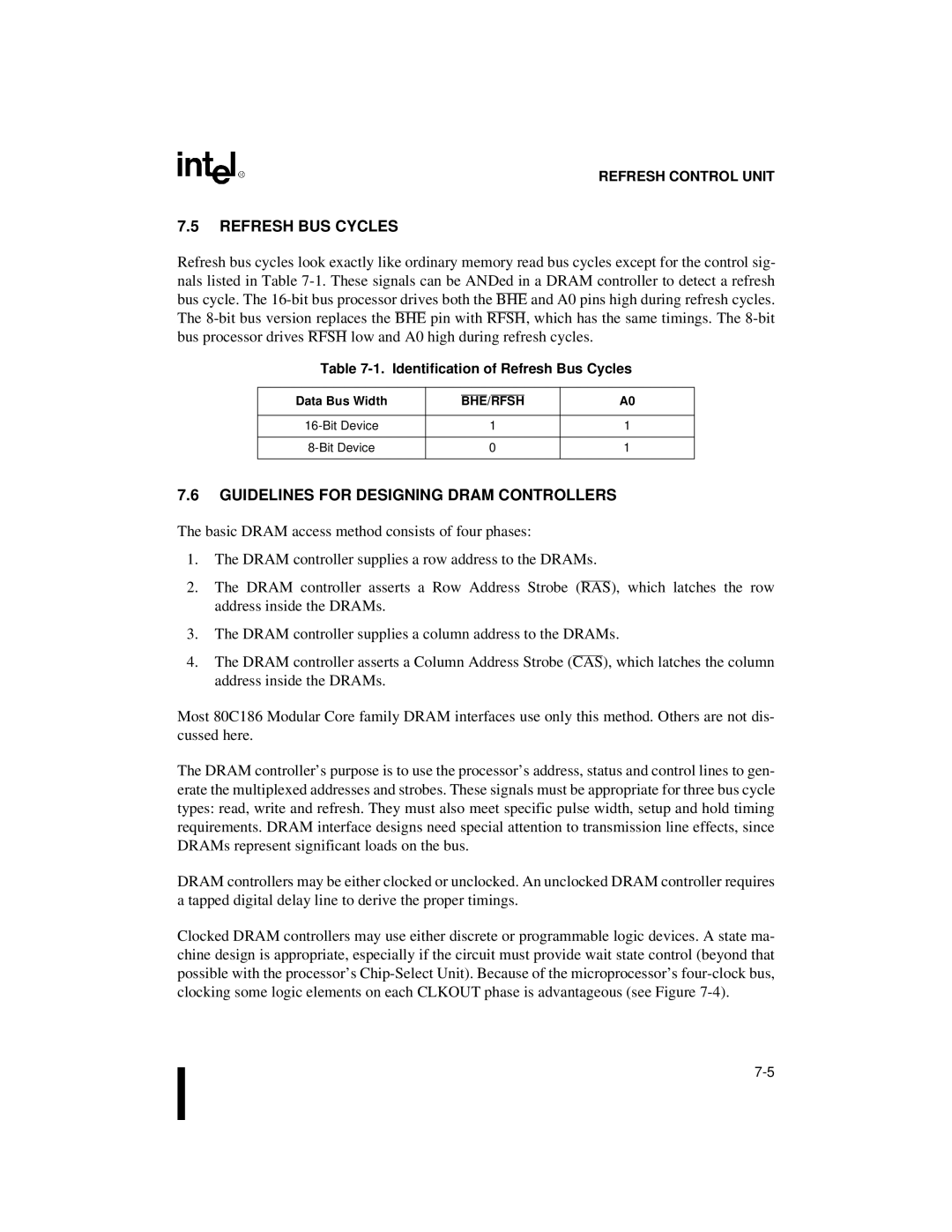

Refresh BUS Cycles

Guidelines for Designing Dram Controllers

Identification of Refresh Bus Cycles

Data Bus Width

Muxed Row Column Address S20

T3/TW Clkout

RAS CAS

Calculating the Refresh Interval

Programming the Refresh Control Unit

Refresh Control Unit Registers

Register NameRefresh Base Address Register

Rfbase

Register FunctionDetermines upper 7 bits of refresh address

Refresh Base Address Register

Rftime

Register Function Sets refresh rate

Refresh Control Register

Rfcon

Controls Refresh Unit operation

Programming Example

Example 7-1. Initializing the Refresh Control Unit

Refresh Operation and BUS Hold

Clkout Hold Hlda DEN

RD, WR BHE, S2 DT / R A1916

Page

Interrupt Control Unit

Page

Chapter Interrupt Control Unit

Functional Overview

Master Mode

Timer 0 Timer 1 Timer

Generic Functions in Master Mode

DMA

Default Interrupt Priorities

Interrupt Masking

Interrupt Priority

Interrupt Name Relative Priority

Interrupt Nesting

Priority Resolution

Functional Operation in Master Mode

Typical Interrupt Sequence

Priority Resolution Example

Cascading with External 8259As

Interrupts That Share a Single Source

INT INT0

Inta INTA0

INT INT1

Inta INTA1

Interrupt Acknowledge Sequence

Polling

Fixed Interrupt Types

Interrupt Name Interrupt Type

Edge and Level Triggering

Additional Latency and Response Time

Inta Idle

Inta Idle Read IP

Read CS Idle Push Flags Push CS Push IP

Programming the Interrupt Control Unit

2CH

Interrupt Control Registers

2AH

Interrupt Control Register for Internal Sources

MSK

I2CON, I3CON

Register NameInterrupt Control Register non-cascadable pins

LVL

Register NameInterrupt Control Register cascadable pins

I0CON, I1CON

Sfnm

CAS

Interrupt Request Register

Register Name Interrupt Request Register Register Mnemonic

Reqst

Register Function Stores pending interrupt requests

Register Name Interrupt Mask Register Register Mnemonic

Imask

Register Function Masks individual interrupt sources

Priority Mask Register

In-Service Register

Priority Mask Register

Primsk

Masks lower-priority interrupt sources

In-Service Register

Inserv

Indicates which interrupt handlers are in process

Poll and Poll Status Registers

Poll

Poll Register

Ireq

Read to check for pending interrupts when polling

Poll Status Register

Pollsts

End-of-Interrupt EOI Register

Used to issue an EOI command

End-of-Interrupt Register

EOI

Interrupt Status Register

Slave Mode

Interrupt Status Register

Intsts

Dhlt

INT0 Inta

IRQ INT VCC

Slave Mode Programming

16. Interrupt Sources in Slave Mode

Slave Mode Fixed Interrupt Type Bits

Master Mode Slave Mode PCB Offset Register Name

Interrupt Vector Register

Interrupt Control Unit Register Comparison

Register NameInterrupt Vector Register Slave Mode only

Intvec

End-of-Interrupt Register in Slave Mode

Used to issue the EOI command

Interrupt Vectoring in Slave Mode

T1 T2 T3 T4

Inta INTA0 Select Lock

CAS20 Slave Cascade Address From 8259A

Initializing the Interrupt Control Unit for Master Mode

Inta Idle Read IP Read CS Push Flags Push CS Push IP

Priorities are used

Page

Timer/Counter Unit

Page

Chapter TIMER/COUNTER Unit

Timer Element Registers Output Latch

Interrupt Latch Clock

Counter Element Multiplexing and Timer Input Synchronization

T0IN T1IN T0OUT T1OUT

Timers 0 and 1 Flow Chart

From

Programming the TIMER/COUNTER Unit

Timer/Counter Unit Output Modes

Defines Timer 0 and 1 operation

Timer 0 and 1 Control Registers

T0CON, T1CON

RTG

EXT

ALT

Cont

Timer 2 Control Register

Defines Timer 2 operation

T2CON

Maximum count. The MC bit must be cleared

Register Name Timer Count Register Register Mnemonic

Register Function Contains the current timer count

T0CNT, T1CNT, T2CNT

C C

Timer Maxcount Compare Registers

Timer 0 and 1 Clock Sources

Clock Sources

Counting Modes

Clock Source

Retriggering

Timer Operation

Timer Retriggering

Pulsed and Variable Duty Cycle Output

Timer Serviced Internal Count Value Maxcount TxOUT Pin

Enabling/Disabling Counters

Input Setup and Hold Timings

Timer Interrupts

Timing

Timer/Counter Unit Application Examples

Synchronization and Maximum Frequency

Real-Time Clock

Square-Wave Generator

Example 9-1. Configuring a Real-Time Clock

Intsts

Out Dx, al

Timer2interruptroutine proc far

Example 9-2. Configuring a Square-Wave Generator

T1CON

Example 9-3. Configuring a Digital One-Shot

Cmpb

Page

Direct Memory Access Unit

Page

Chapter Direct Memory Access Unit

DMA Transfer

Fetch Deposit

Typical DMA Transfer

Source and Destination Pointers

DMA Requests

DMA Transfer Directions

Byte and Word Transfers

External Requests

T1 or T2 or T3 or TW or T4 or

Cycle

DRQ

DRQ Case

Source Synchronization

Timer 2-Initiated Transfers

Fetch Cycle Deposit Cycle T1 T2 T3 T4 T1 T2 T3 T4 TI TI

Clkout DRQ

Case

DMA Transfer Counts

Termination and Suspension of DMA Transfers

DMA Unit Interrupts

DMA Cycles and the BIU

Two-Channel DMA Unit

DMA Channel Arbitration

Module

Two-Channel DMA Module

Programming the DMA Unit

SRC

DMA Channel Parameters

Register Mnemonic DxSRCH

Register NameDMA Source Address Pointer High

DMA Xxxxh

Register Mnemonic DxSRCL

Register NameDMA Source Address Pointer Low

S S a a

DxDSTH

Register NameDMA Destination Address Pointer High

Contains the upper 4 bits of the DMA Destination pointer

Register NameDMA Destination Address Pointer Low

Register Mnemonic DxDSTL

D I E N C C C N T

Dmem

Ddec

Dinc

Synchronization Type

Idrq

Strt

CHG

Word

Selecting Channel Synchronization

Arming the DMA Channel

Programming the Transfer Count Options

Setting the Relative Priority of a Channel

Generating Interrupts on Terminal Count

Suspension of DMA Transfers

Initializing the DMA Unit

Hardware Considerations and the DMA Unit

DRQ Pin Timing Requirements

DMA Latency

DMA Transfer Rates

Generating a DMA Acknowledge

DMA Unit Examples

Example 10-1. Initializing the DMA Unit

MOV DS, AX Assume Dsdataseg

10-24

10-25

Example 10-2. Timed DMA Transfers

10-27

Page

Math Coprocessing

Page

Overview of Math Coprocessing

Availability of Math Coprocessing

80C187 Math Coprocessor

11.3.1 80C187 Instruction Set

C187 Data Transfer Instructions

Real Transfers

Integer Transfers

Packed Decimal Transfers

C187 Arithmetic Instructions

Other Operations

Comparison Instructions

C187 Comparison Instructions

Transcendental Instructions

C187 Transcendental Instructions

Constant Instructions

C187 Constant Instructions

C187 Processor Control Instructions

Fldz FLD1 Fldpi FLDL2T FLDL2E FLDLG2 FLDLN2

11.3.2 80C187 Data Types

Microprocessor and Coprocessor Operation

C187-Supported Data Types

Modular Core

80C187

80C186

Processor Bus Cycles Accessing the 80C187

Clocking the 80C187

C187 I/O Port Assignments

Address Read Definition Write Definition

System Design Tips

C187 Configuration with a Partially Buffered Bus

Exception Trapping

Example Math Coprocessor Routines

80C186 Modular Core

C187 Exception Trapping via Processor Interrupt Pin

Name Example80C187init

Example 11-2. Floating Point Math Routine Using Fsincos

Results

Once Mode

Page

Chapter Once Mode

ENTERING/LEAVING Once Mode

RES UCS LCS

Oscout

80C186 Instruction Set Additions Extensions

Page

80C186 Instruction SET Additions

Data Transfer Instructions

String Instructions

High-Level Instructions

Figure A-1. Formal Definition of Enter

Figure A-2. Variable Access in Nested Procedures

Figure A-4. Stack Frame for Procedure a at Level

BPM BPA BPB

Leave

Bound register, address

80C186 Instruction SET Enhancements

Bit Manipulation Instructions

Arithmetic Instructions

Shift Instructions

ROL destination, count

Rotate Instructions

Input Synchronization

Page

WHY Synchronizers are Required

Figure B-1. Input Synchronization Circuit

Asynchronous Pins

Instruction Set Descriptions

Page

Table C-1. Instruction Format Variables

Variable Description

Table C-2. Instruction Operands

Operand Description

Table C-3. Flag Bit Functions

Table C-4. Instruction Set

Ascii Adjust for Subtraction

AAS

ADC

Add with Carry

ADD

ADD dest, src

Logical

Dest, src

Call Procedure

Call procedure-name

Bound

Detect Value Out of Range

Clear Carry flag

Convert Byte to Word

Clear Direction flag

Clear Interrupt-enable Flag

Complement Carry Flag

CMP

Compare

CMP dest, src

Compare String

Decimal Adjust for Subtraction

Decimal Adjust for Addition

Convert Word to Doubleword

DEC

Decrement

Divide When Source Operand is a Byte

When Source Operand is a Word

Enter locals, levels

Procedure Entry

Escape

Halt

Integer Divide When Source Operand is a Byte

Integer Multiply When Source Operand is a Byte

Input Byte or Word When Source Operand is a Byte

Imul

Accum, port

INC

Increment

String

INS dest-string, port

Interrupt

INT interrupt-type

Interrupt on Overflow

Interrupt Return

Jump on Above

Jump on Not Below or Equal

Jump on Above or Equal

Jump on Not Below

Jump on Below

Jump on Not Above or Equal

Jump if CX Zero

Jump on Equal Jump on Zero

Jump on Greater Than

Jump on Not Less Than or Equal

Name Description Operation Flags Affected Jump on Less Than

Jump on Not Greater Than or Equal

Jump on Less Than or Equal

Jump on Not Greater Than

Jump on Not Equal

Jump on Not Zero

Jump on Not Overflow

Jump on Not Sign

Name Description Operation Flags Affected Jump on Overflow

Jump on Parity

Jump on Parity Equal

Instruction Format

Load Pointer Using DS

LDS dest, src

Load Effective Address

LEA dest, src

LES dest, src

Load Pointer Using ES

Lock the Bus

Load String Byte or Word When Source Operand is a Byte

Lods src-string

Loop

Loop While Equal

Loop While Not Equal

Loop While Not Zero

Move Byte or Word

MOV dest, src

Multiply When Source Operand is a Byte

Move String

Movs dest-string, src-string

MUL

Logical Not When Source Operand is a Byte

Negate When Source Operand is a Byte

NEG

Name Description Operation Flags Affected Logical or

Or dest,src

Output

OUT port, accumulator

Outs port, srcstring

Out String

Pop

Pop Flags

Pop All

Push

Push All

Push Flags

Rotate Through Carry Left

RCL dest, count

Rotate Through Carry Right

RCR dest, count

Repeat

Repeat While Equal

Repeat While Zero

Repeat While Not Equal

RET

Return

RET optional-pop-value

Rotate Left

ROR dest, count

Rotate Right

Store Register AH Into Flags

Shift Arithmetic Left

Shift Logical Left

Shift Arithmetic Right

Subtract With Borrow

SBB

SBB dest, src

Scan String When Source Operand is a Byte

Scas dest-string

Shift Logical Right

SHR dest, src

Set Carry Flag

Set Direction Flag

Store Byte or Word String When Source Operand is a Byte

Set Interrupt-enable Flag

Stos dest-string

SUB

Subtract

SUB dest, src

Test

Exchange

Wait

Xchg dest, src

Translate

Xlat translate-table

Exclusive Or

XOR dest, src

Page

Instruction Set Opcodes and Clock Cycles

Page

Table D-1. Operand Variables

EA Calculation

Mod Effect on EA Calculation

Reg Bit w=1 Bit w=0

Table D-2. Instruction Set Summary

Function Format Clocks

Arithmetic Instructions

Arithmetic Instructions

BIT Manipulation Instructions

String Manipulation Instructions

JB/JNAE =

LOOPNZ/LOOPNE =

Table D-3. Machine Instruction Decoding Guide

Processor Control Instructions

Instruction SET Opcodes and Clock Cycles

Instruction SET Opcodes and Clock Cycles

Instruction SET Opcodes and Clock Cycles

Instruction SET Opcodes and Clock Cycles

AX,CX

Instruction SET Opcodes and Clock Cycles

Instruction SET Opcodes and Clock Cycles

Instruction SET Opcodes and Clock Cycles

AL,DX

Instruction SET Opcodes and Clock Cycles

Table D-4. Mnemonic Encoding Matrix Left Half

Table D-4. Mnemonic Encoding Matrix Right Half

Table D-5. Abbreviations for Mnemonic Encoding Matrix

Abbr Definition

Index

Page

Index

Index-2

Index-3

Index-4

Index-5

Index-6

Index-7

Index-8