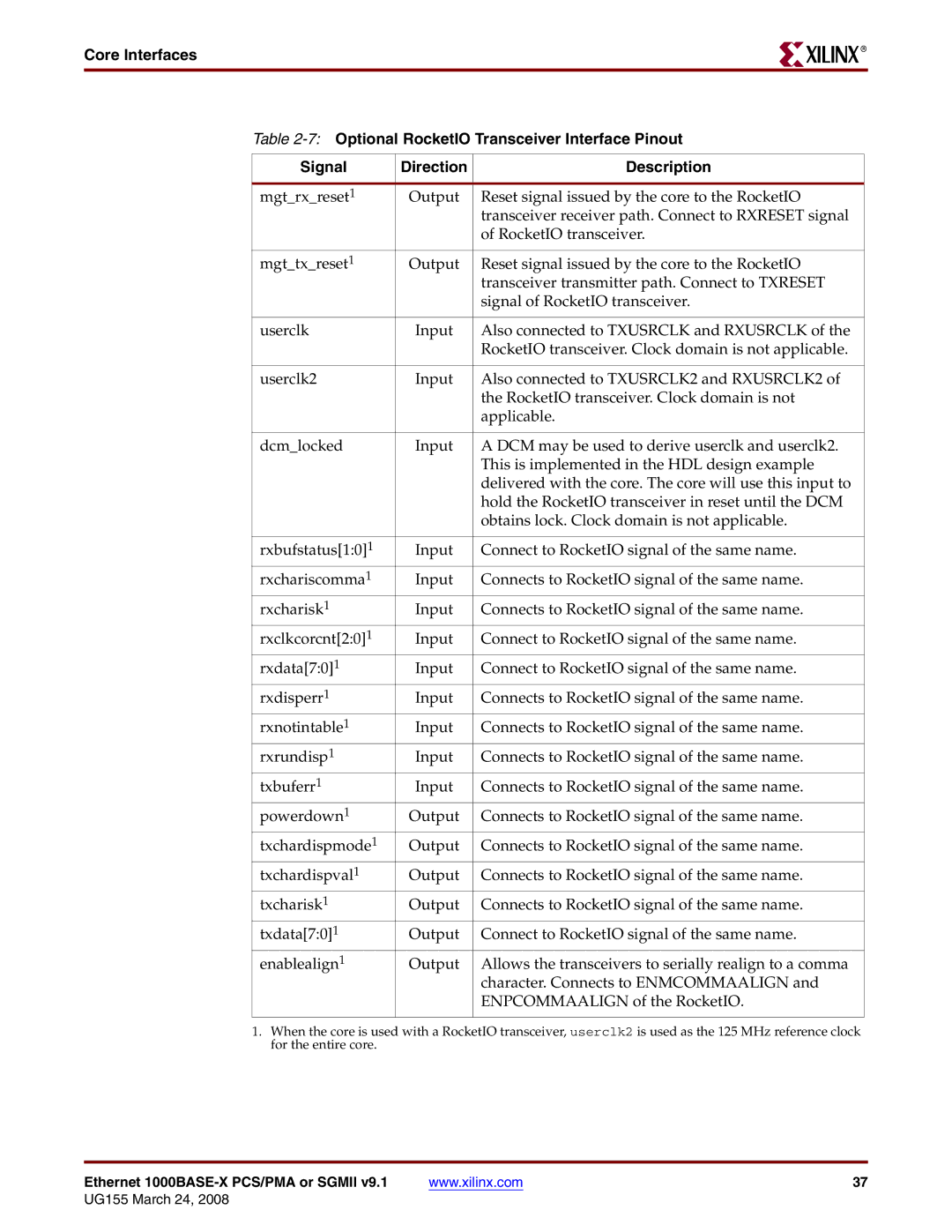

Core Interfaces

Table

R

Signal | Direction | Description |

|

|

|

mgt_rx_reset1 | Output | Reset signal issued by the core to the RocketIO |

|

| transceiver receiver path. Connect to RXRESET signal |

|

| of RocketIO transceiver. |

|

|

|

mgt_tx_reset1 | Output | Reset signal issued by the core to the RocketIO |

|

| transceiver transmitter path. Connect to TXRESET |

|

| signal of RocketIO transceiver. |

|

|

|

userclk | Input | Also connected to TXUSRCLK and RXUSRCLK of the |

|

| RocketIO transceiver. Clock domain is not applicable. |

|

|

|

userclk2 | Input | Also connected to TXUSRCLK2 and RXUSRCLK2 of |

|

| the RocketIO transceiver. Clock domain is not |

|

| applicable. |

|

|

|

dcm_locked | Input | A DCM may be used to derive userclk and userclk2. |

|

| This is implemented in the HDL design example |

|

| delivered with the core. The core will use this input to |

|

| hold the RocketIO transceiver in reset until the DCM |

|

| obtains lock. Clock domain is not applicable. |

|

|

|

rxbufstatus[1:0]1 | Input | Connect to RocketIO signal of the same name. |

rxchariscomma1 | Input | Connects to RocketIO signal of the same name. |

rxcharisk1 | Input | Connects to RocketIO signal of the same name. |

rxclkcorcnt[2:0]1 | Input | Connect to RocketIO signal of the same name. |

rxdata[7:0]1 | Input | Connect to RocketIO signal of the same name. |

rxdisperr1 | Input | Connects to RocketIO signal of the same name. |

rxnotintable1 | Input | Connects to RocketIO signal of the same name. |

rxrundisp1 | Input | Connects to RocketIO signal of the same name. |

txbuferr1 | Input | Connects to RocketIO signal of the same name. |

powerdown1 | Output | Connects to RocketIO signal of the same name. |

txchardispmode1 | Output | Connects to RocketIO signal of the same name. |

txchardispval1 | Output | Connects to RocketIO signal of the same name. |

txcharisk1 | Output | Connects to RocketIO signal of the same name. |

txdata[7:0]1 | Output | Connect to RocketIO signal of the same name. |

enablealign1 | Output | Allows the transceivers to serially realign to a comma |

|

| character. Connects to ENMCOMMAALIGN and |

|

| ENPCOMMAALIGN of the RocketIO. |

|

|

|

1.When the core is used with a RocketIO transceiver, userclk2 is used as the 125 MHz reference clock for the entire core.

Ethernet | www.xilinx.com | 37 |