R

Chapter 6: The Ten-Bit Interface

IOB LOGIC |

|

|

|

IBUFG | gtx_clk_ibufg | BUFG | |

gtx_clk |

| gtx_clk_bufg | |

IPAD | (125 MHz) |

| |

|

|

| |

component_name_block (Block Level from example design)

|

|

| IOB LOGIC |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Ethernet |

| FDDRRSE |

|

|

|

| ||

or SGMII LogiCORE |

|

|

|

|

|

|

| |

'0' | D | Q |

|

|

|

| ||

|

|

|

|

|

| |||

gtx_clk |

|

|

| OBUF | ||||

|

| pma_tx_clk_obuf |

|

| pma_tx_clk | |||

|

|

|

|

|

|

| OPAD | |

'1' | D | Q |

|

|

| |||

|

|

|

| |||||

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| OBUF | |

| tx_code_group_int[0] |

|

| tx_code_group_reg[0] |

| tx_code_group[0] |

tx_code_group[0] |

| D Q |

| OPAD | ||

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| OBUF | |

tx_code_group[9] | tx_code_group_int[9] |

|

| tx_code_group_reg[9] |

| tx_code_group[9] |

| D Q |

| OPAD | |||

|

|

|

| |||

|

| |||||

|

|

|

|

|

|

|

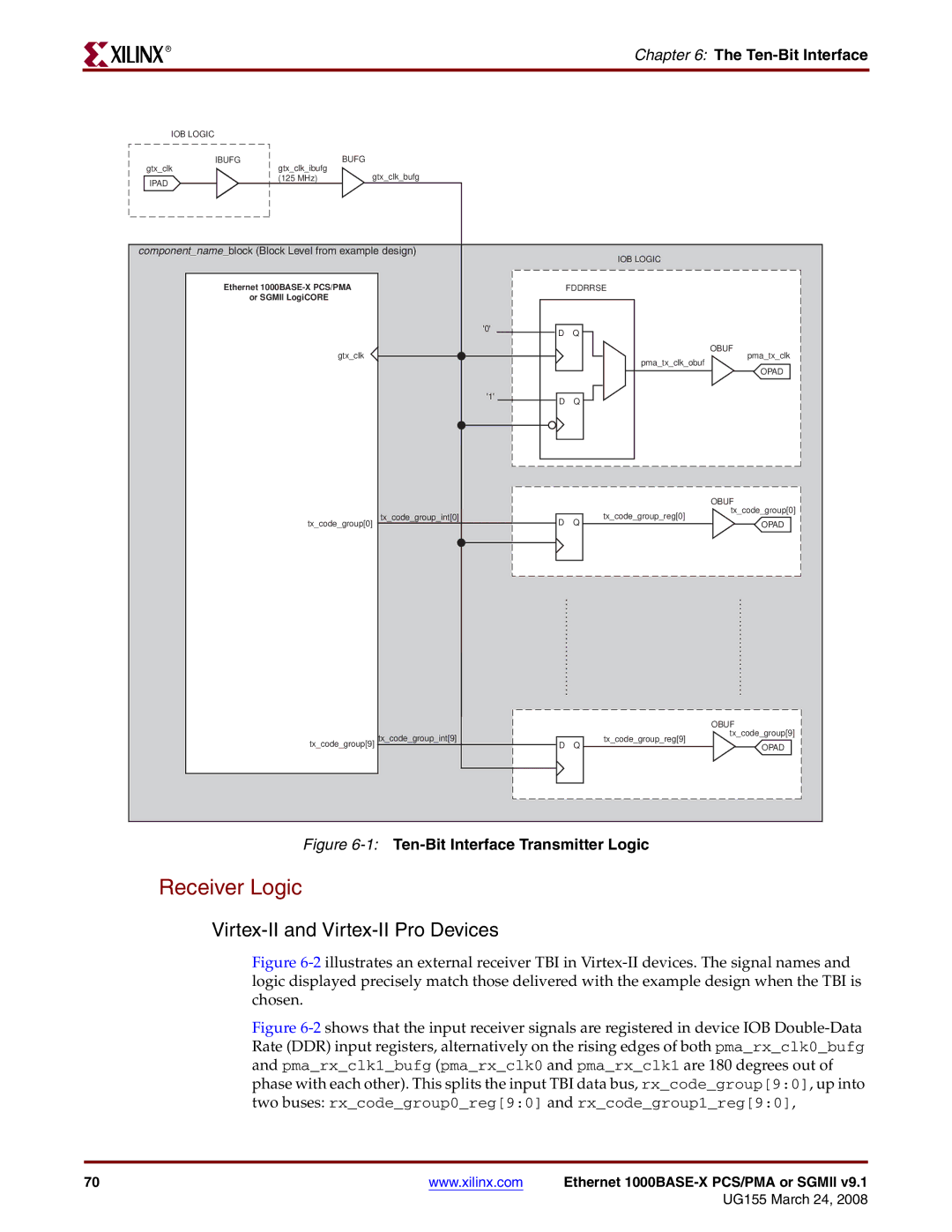

Figure 6-1: Ten-Bit Interface Transmitter Logic

Receiver Logic

Virtex-II and Virtex-II Pro Devices

Figure 6-2 illustrates an external receiver TBI in Virtex-II devices. The signal names and logic displayed precisely match those delivered with the example design when the TBI is chosen.

Figure 6-2 shows that the input receiver signals are registered in device IOB Double-Data Rate (DDR) input registers, alternatively on the rising edges of both pma_rx_clk0_bufg and pma_rx_clk1_bufg (pma_rx_clk0 and pma_rx_clk1 are 180 degrees out of phase with each other). This splits the input TBI data bus, rx_code_group[9:0], up into two buses: rx_code_group0_reg[9:0] and rx_code_group1_reg[9:0],

70 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |