R

Chapter 2: Core Architecture

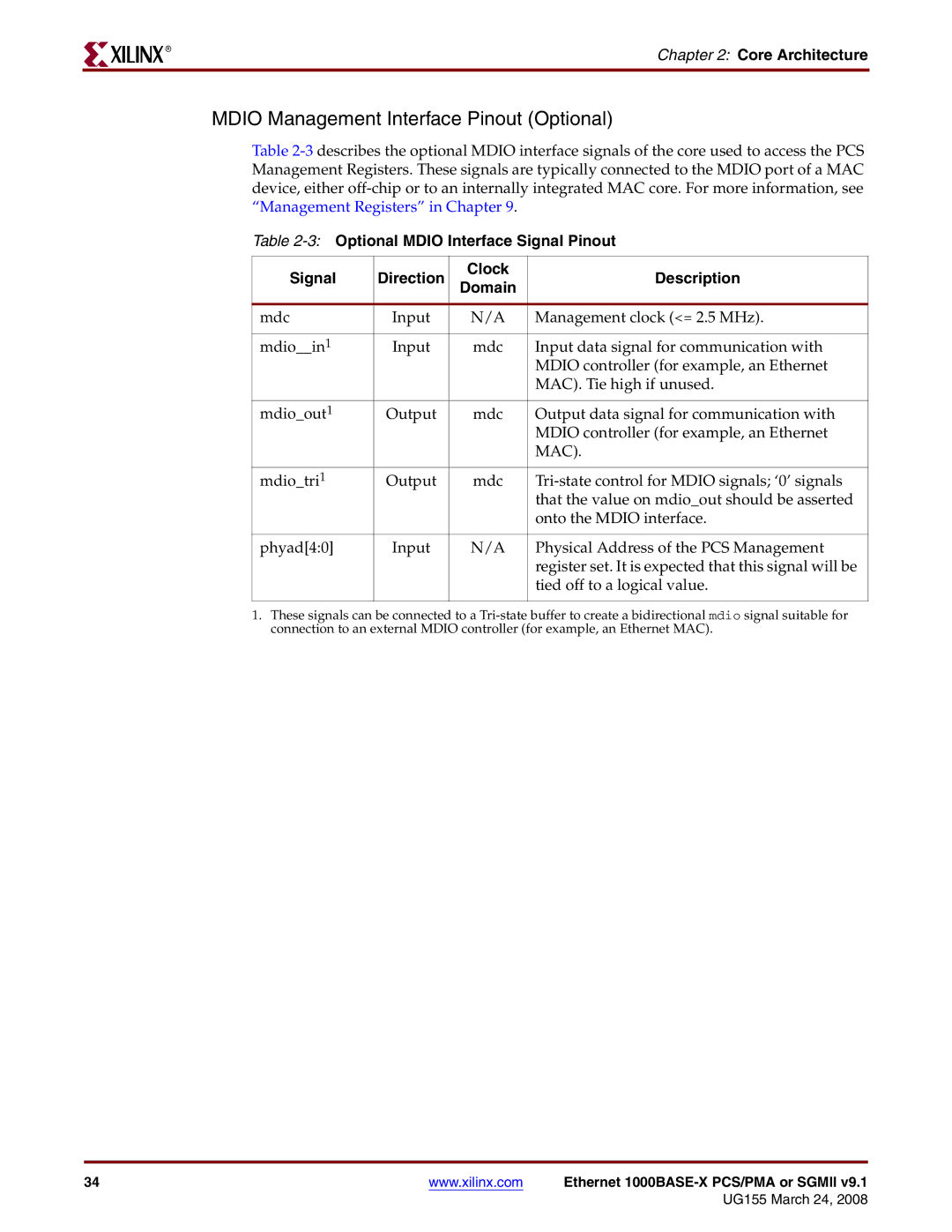

MDIO Management Interface Pinout (Optional)

Table

Table

Signal | Direction | Clock | Description |

Domain | |||

|

|

|

|

mdc | Input | N/A | Management clock (<= 2.5 MHz). |

|

|

|

|

mdio__in1 | Input | mdc | Input data signal for communication with |

|

|

| MDIO controller (for example, an Ethernet |

|

|

| MAC). Tie high if unused. |

|

|

|

|

mdio_out1 | Output | mdc | Output data signal for communication with |

|

|

| MDIO controller (for example, an Ethernet |

|

|

| MAC). |

|

|

|

|

mdio_tri1 | Output | mdc | |

|

|

| that the value on mdio_out should be asserted |

|

|

| onto the MDIO interface. |

|

|

|

|

phyad[4:0] | Input | N/A | Physical Address of the PCS Management |

|

|

| register set. It is expected that this signal will be |

|

|

| tied off to a logical value. |

|

|

|

|

1.These signals can be connected to a

34 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |