R

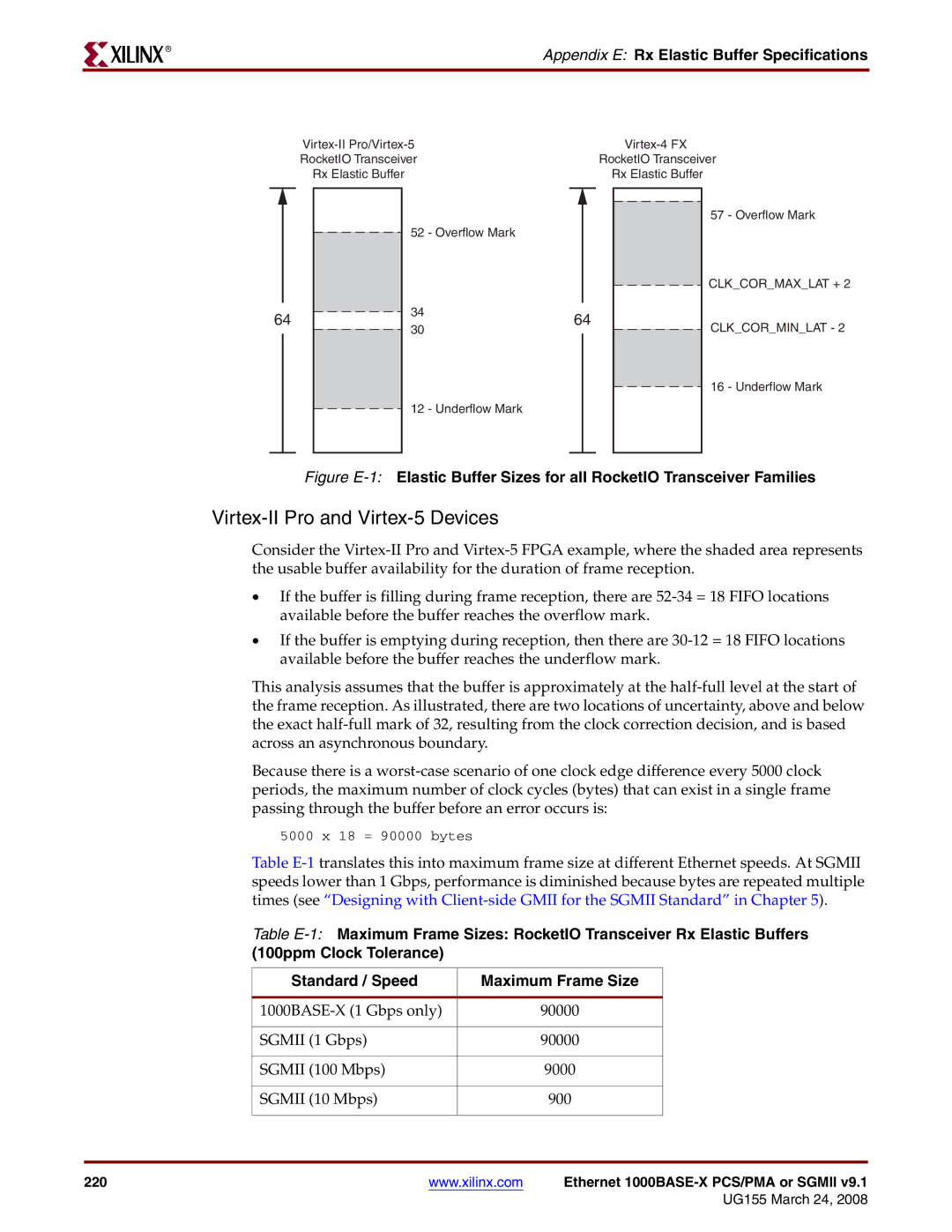

Appendix E: Rx Elastic Buffer Specifications

| ||

RocketIO Transceiver |

| RocketIO Transceiver |

Rx Elastic Buffer |

| Rx Elastic Buffer |

|

|

|

52 - Overflow Mark

57 - Overflow Mark

CLK_COR_MAX_LAT + 2

64

34

30

64

CLK_COR_MIN_LAT - 2

16 - Underflow Mark

12 - Underflow Mark

Figure E-1: Elastic Buffer Sizes for all RocketIO Transceiver Families

Virtex-II Pro and Virtex-5 Devices

Consider the

•If the buffer is filling during frame reception, there are

•If the buffer is emptying during reception, then there are

This analysis assumes that the buffer is approximately at the

Because there is a

5000 x 18 = 90000 bytes

Table

Table

Standard / Speed | Maximum Frame Size |

90000 | |

SGMII (1 Gbps) | 90000 |

SGMII (100 Mbps) | 9000 |

SGMII (10 Mbps) | 900 |

220 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |