R

Chapter 2: Core Architecture

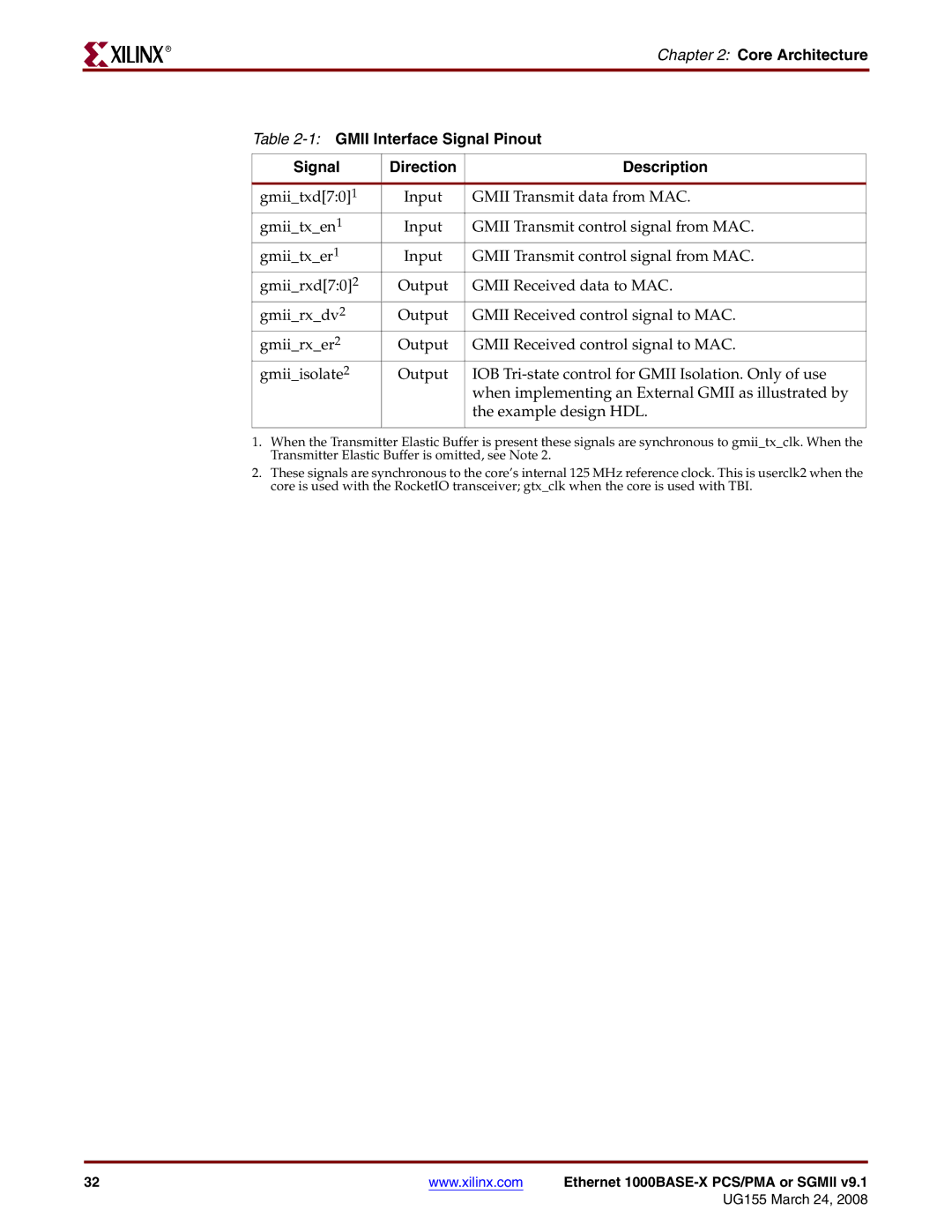

Table

Signal | Direction | Description |

|

|

|

gmii_txd[7:0]1 | Input | GMII Transmit data from MAC. |

gmii_tx_en1 | Input | GMII Transmit control signal from MAC. |

gmii_tx_er1 | Input | GMII Transmit control signal from MAC. |

gmii_rxd[7:0]2 | Output | GMII Received data to MAC. |

gmii_rx_dv2 | Output | GMII Received control signal to MAC. |

gmii_rx_er2 | Output | GMII Received control signal to MAC. |

gmii_isolate2 | Output | IOB |

|

| when implementing an External GMII as illustrated by |

|

| the example design HDL. |

|

|

|

1.When the Transmitter Elastic Buffer is present these signals are synchronous to gmii_tx_clk. When the Transmitter Elastic Buffer is omitted, see Note 2.

2.These signals are synchronous to the core’s internal 125 MHz reference clock. This is userclk2 when the core is used with the RocketIO transceiver; gtx_clk when the core is used with TBI.

32 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |