R

Chapter 2: Core Architecture

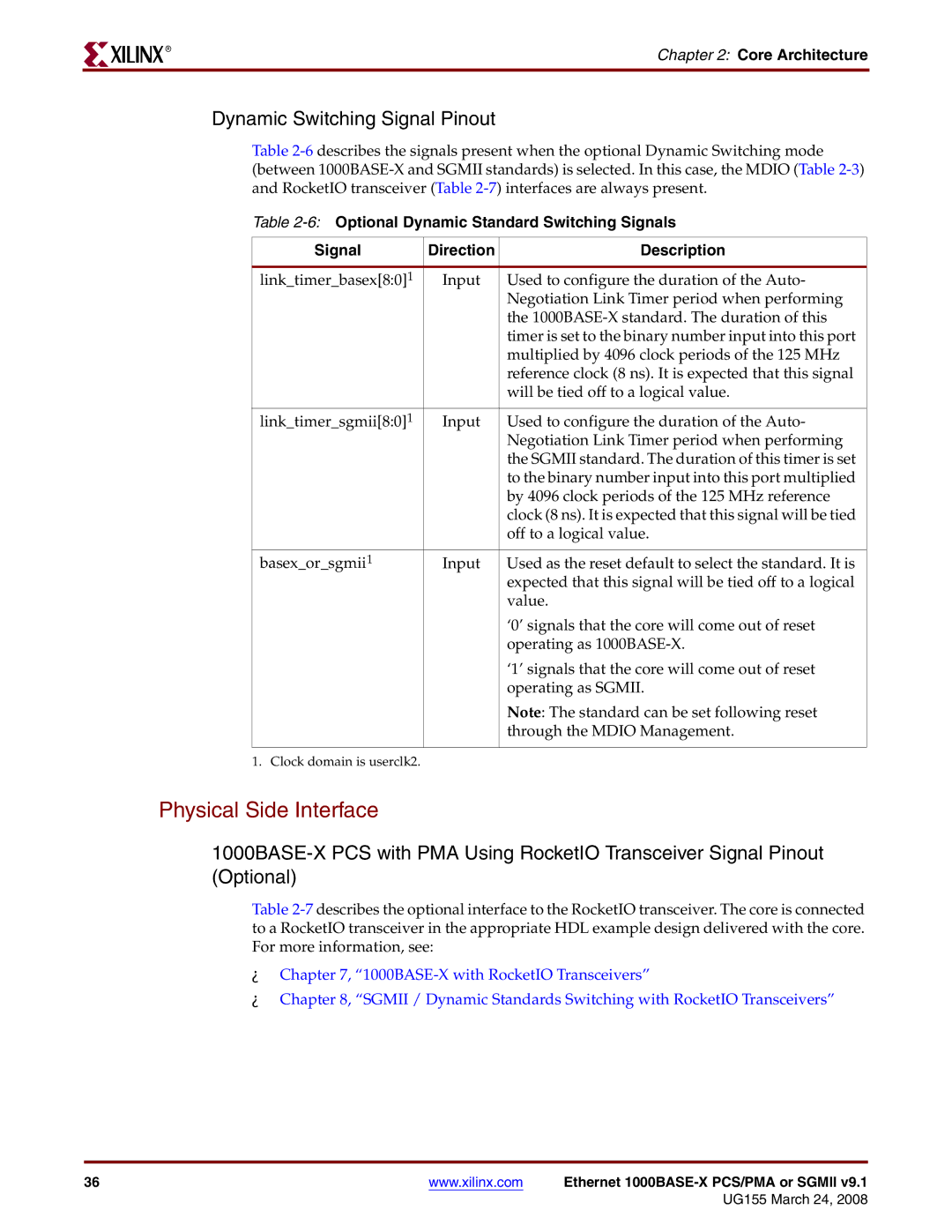

Dynamic Switching Signal Pinout

Table

Table

Signal | Direction | Description |

|

|

|

link_timer_basex[8:0]1 | Input | Used to configure the duration of the Auto- |

|

| Negotiation Link Timer period when performing |

|

| the |

|

| timer is set to the binary number input into this port |

|

| multiplied by 4096 clock periods of the 125 MHz |

|

| reference clock (8 ns). It is expected that this signal |

|

| will be tied off to a logical value. |

|

|

|

link_timer_sgmii[8:0]1 | Input | Used to configure the duration of the Auto- |

|

| Negotiation Link Timer period when performing |

|

| the SGMII standard. The duration of this timer is set |

|

| to the binary number input into this port multiplied |

|

| by 4096 clock periods of the 125 MHz reference |

|

| clock (8 ns). It is expected that this signal will be tied |

|

| off to a logical value. |

|

|

|

basex_or_sgmii1 | Input | Used as the reset default to select the standard. It is |

|

| expected that this signal will be tied off to a logical |

|

| value. |

|

| ‘0’ signals that the core will come out of reset |

|

| operating as |

|

| ‘1’ signals that the core will come out of reset |

|

| operating as SGMII. |

|

| Note: The standard can be set following reset |

|

| through the MDIO Management. |

|

|

|

1. Clock domain is userclk2.

Physical Side Interface

Table

•Chapter 7,

•Chapter 8, “SGMII / Dynamic Standards Switching with RocketIO Transceivers”

36 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |