Clock Sharing Across Multiple Cores with RocketIO

R

Clock Sharing Across Multiple Cores with RocketIO

Virtex-II Pro Devices

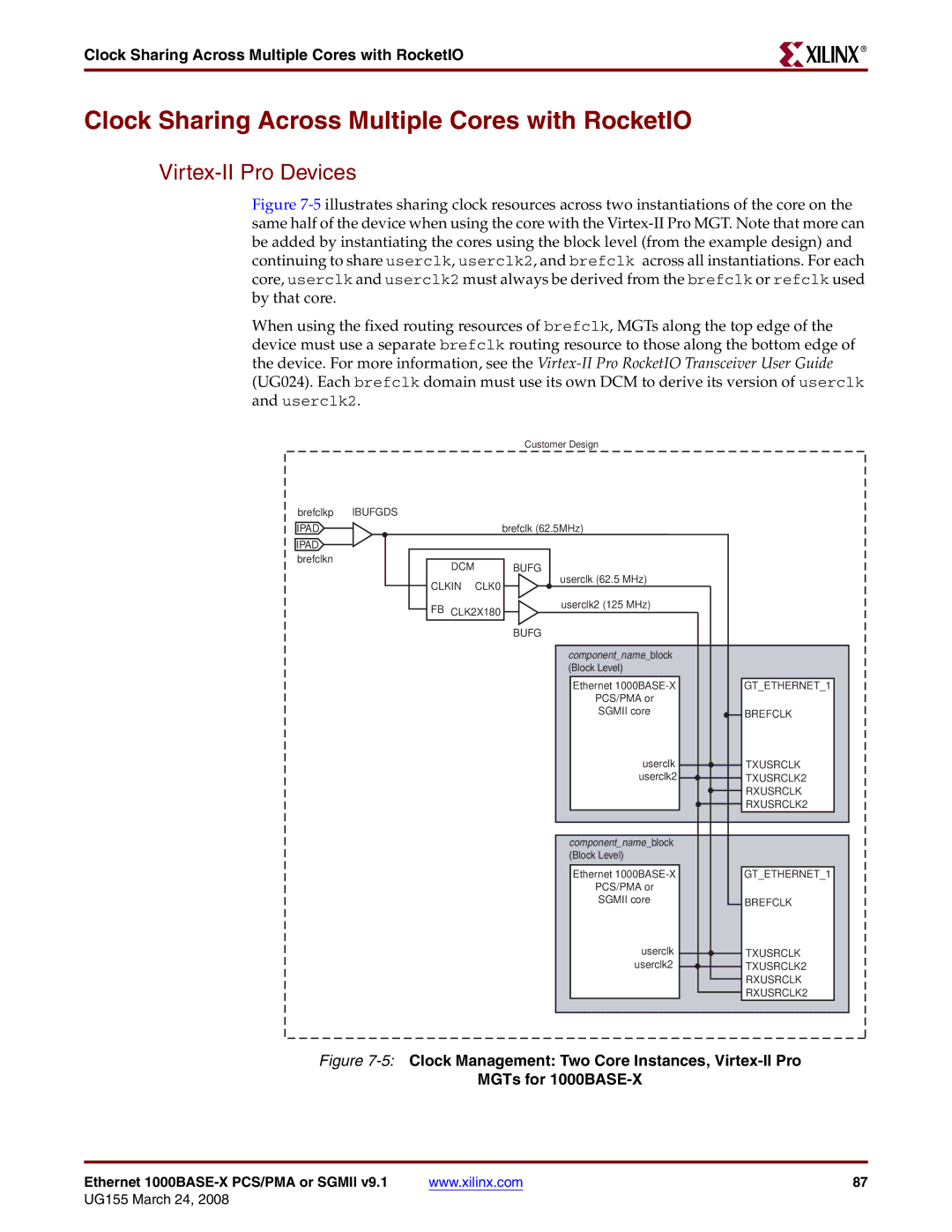

Figure 7-5 illustrates sharing clock resources across two instantiations of the core on the same half of the device when using the core with the Virtex-II Pro MGT. Note that more can be added by instantiating the cores using the block level (from the example design) and continuing to share userclk, userclk2, and brefclk across all instantiations. For each core, userclk and userclk2 must always be derived from the brefclk or refclk used by that core.

When using the fixed routing resources of brefclk, MGTs along the top edge of the device must use a separate brefclk routing resource to those along the bottom edge of the device. For more information, see the Virtex-II Pro RocketIO Transceiver User Guide (UG024). Each brefclk domain must use its own DCM to derive its version of userclk and userclk2.

Customer Design

brefclkp IBUFGDS IPAD

IPAD brefclkn

|

| brefclk (62.5MHz) |

|

|

|

DCM |

| BUFG |

CLKIN | CLK0 | userclk (62.5 MHz) |

| ||

FB CLK2X180 | userclk2 (125 MHz) | |

| ||

|

| BUFG |

component_name_block (Block Level)

| Ethernet |

| GT_ETHERNET_1 |

|

| PCS/PMA or |

|

|

|

| SGMII core |

| BREFCLK |

|

| userclk |

| TXUSRCLK |

|

| ||||

| userclk2 |

| TXUSRCLK2 |

|

|

|

| RXUSRCLK |

|

|

|

| RXUSRCLK2 |

|

|

|

|

|

|

|

|

|

|

|

component_name_block |

|

|

| |

(Block Level) |

|

|

| |

Ethernet

PCS/PMA or

SGMII core

userclk userclk2

GT_ETHERNET_1

BREFCLK

TXUSRCLK

TXUSRCLK2

RXUSRCLK

RXUSRCLK2

Figure 7-5: Clock Management: Two Core Instances, Virtex-II Pro

MGTs for 1000BASE-X

Ethernet | www.xilinx.com | 87 |