System Overview

R

Optional PCS Management Registers

Configuration and status of the core, including access to and from the optional Auto- Negotiation function, uses the

802.3clause 37. These registers are accessed through the serial Management Data Input/Output Interface (MDIO), defined in IEEE 802.3 clause 22, as if it were an externally connected PHY.

The PCS Management Registers may be omitted from the core when the core is performing the

When the core is performing the SGMII standard, the PCS Management Registers become mandatory and information in the registers takes on a different interpretation. For more information, see “Management Registers” in Chapter 9.

RocketIO Interface Block

The RocketIO Interface Block enables the core to connect to a

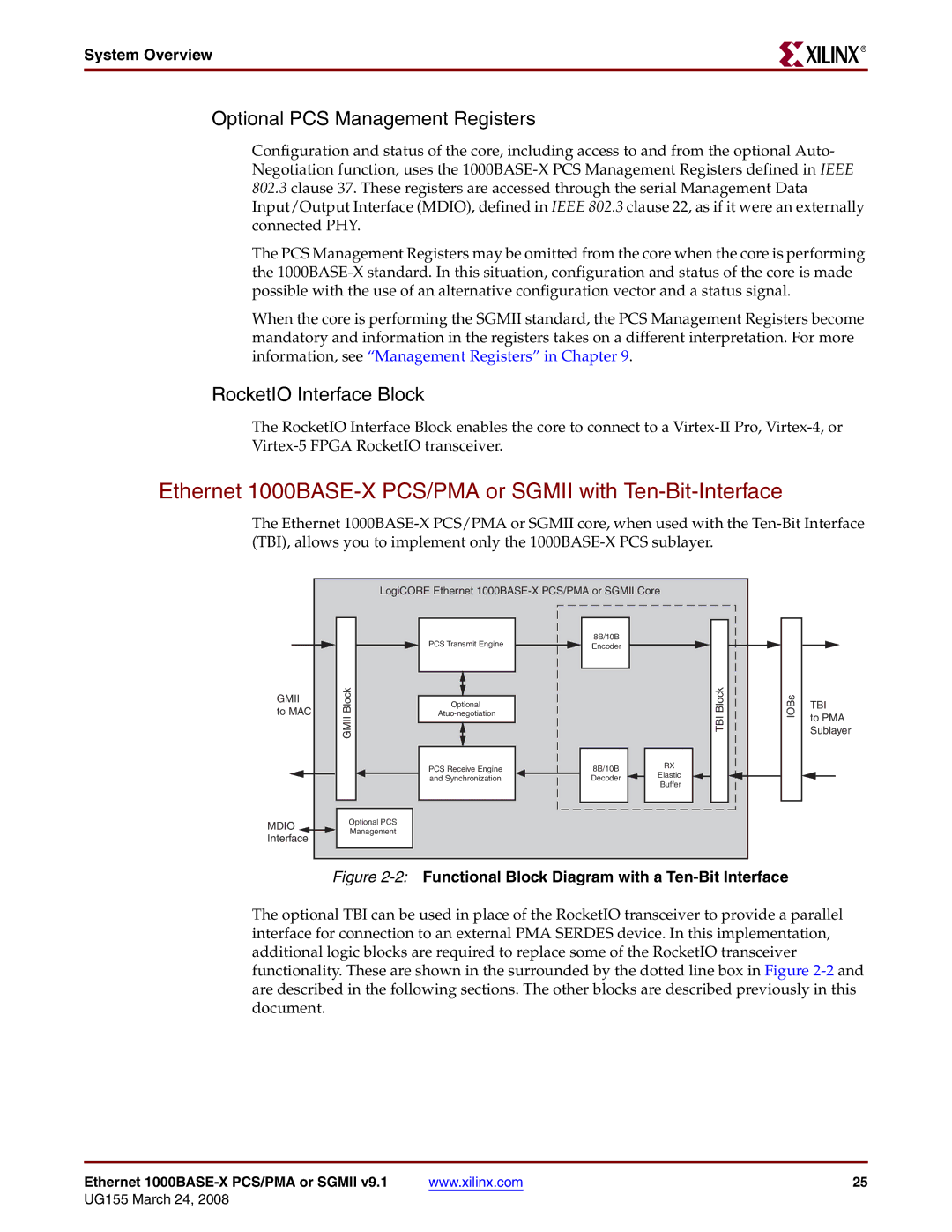

Ethernet 1000BASE-X PCS/PMA or SGMII with Ten-Bit-Interface

The Ethernet

| LogiCORE Ethernet |

|

| |||

|

| PCS Transmit Engine | 8B/10B |

|

|

|

|

| Encoder |

|

|

| |

GMII | BlockGMII | Optional |

| BlockTBI | IOBs | TBI |

|

|

|

| |||

to MAC |

|

|

|

| ||

|

|

|

| to PMA | ||

|

|

|

|

|

| |

|

|

|

|

|

| Sublayer |

|

| PCS Receive Engine | 8B/10B | RX |

|

|

|

| Elastic |

|

| ||

|

| and Synchronization | Decoder |

|

| |

|

| Buffer |

|

| ||

|

|

|

|

|

| |

MDIO | Optional PCS |

|

|

|

|

|

Management |

|

|

|

|

| |

Interface |

|

|

|

|

| |

|

|

|

|

|

| |

| Figure | Functional Block Diagram with a |

| |||

The optional TBI can be used in place of the RocketIO transceiver to provide a parallel interface for connection to an external PMA SERDES device. In this implementation, additional logic blocks are required to replace some of the RocketIO transceiver functionality. These are shown in the surrounded by the dotted line box in Figure

Ethernet | www.xilinx.com | 25 |