R

Chapter 3: Generating and Customizing the Core

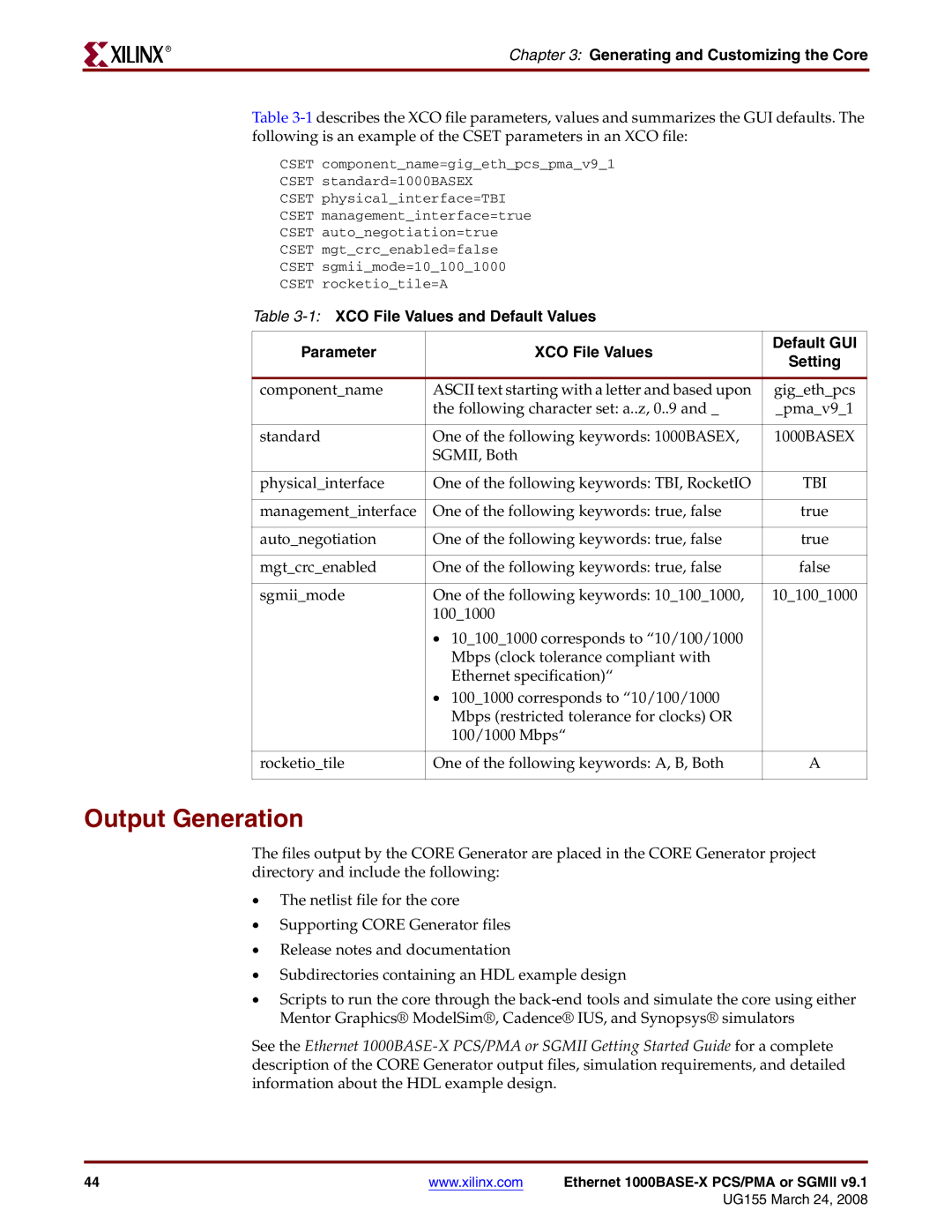

Table

CSET component_name=gig_eth_pcs_pma_v9_1

CSET standard=1000BASEX

CSET physical_interface=TBI

CSET management_interface=true

CSET auto_negotiation=true

CSET mgt_crc_enabled=false

CSET sgmii_mode=10_100_1000

CSET rocketio_tile=A

Table

Parameter | XCO File Values | Default GUI | |

Setting | |||

|

| ||

|

|

| |

component_name | ASCII text starting with a letter and based upon | gig_eth_pcs | |

| the following character set: a..z, 0..9 and _ | _pma_v9_1 | |

|

|

| |

standard | One of the following keywords: 1000BASEX, | 1000BASEX | |

| SGMII, Both |

| |

|

|

| |

physical_interface | One of the following keywords: TBI, RocketIO | TBI | |

|

|

| |

management_interface | One of the following keywords: true, false | true | |

|

|

| |

auto_negotiation | One of the following keywords: true, false | true | |

|

|

| |

mgt_crc_enabled | One of the following keywords: true, false | false | |

|

|

| |

sgmii_mode | One of the following keywords: 10_100_1000, | 10_100_1000 | |

| 100_1000 |

| |

| • 10_100_1000 corresponds to “10/100/1000 |

| |

| Mbps (clock tolerance compliant with |

| |

| Ethernet specification)“ |

| |

| • 100_1000 corresponds to “10/100/1000 |

| |

| Mbps (restricted tolerance for clocks) OR |

| |

| 100/1000 Mbps“ |

| |

|

|

| |

rocketio_tile | One of the following keywords: A, B, Both | A | |

|

|

|

Output Generation

The files output by the CORE Generator are placed in the CORE Generator project directory and include the following:

•The netlist file for the core

•Supporting CORE Generator files

•Release notes and documentation

•Subdirectories containing an HDL example design

•Scripts to run the core through the

See the Ethernet

44 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |